# HITFET<sup>™</sup> + Configurations

## From fully featured to standard low-side

#### Scope and purpose

HITFET<sup>™</sup> + devices propose various features compared to a standard low-side switch, including more pins for diagnostic signal to micro-controller, adjustable slew-rate for best trade-off between Electro Magnetic Interference (EMI) and power losses, high inrush current capability, active free-wheeling and very low leakage in OFF state. When some features are not needed, pin count can be reduced. This application note shows the recommended configurations.

#### **Intended audience**

This document is targeted for all electronics design engineers who need HITFET<sup>™</sup> + low-side power switches in applications where pin count has to be kept minimal.

#### **Table of contents**

## 1

## Table of contents

## Contents

| 1   | Table of contents                                                         | 2  |

|-----|---------------------------------------------------------------------------|----|

| 2   | BTS3xxxEJ recommended configurations                                      | 3  |

| 2.1 | Pinout reminder                                                           | .3 |

| 2.2 | Analysis of possible configurations                                       | .4 |

| 3   | BTF3xxxEJ recommended configurations                                      | 5  |

| 3.1 | Quick find page                                                           | .5 |

| 3.2 | Pinout reminder                                                           | .6 |

| 3.3 | Full feature configuration analysis – 3 pins available on microcontroller | .7 |

| 3.4 | Configurations when 2 pins from microcontroller available                 | .8 |

| 3.5 | Configurations when only 1 pin from microcontroller is available          | LO |

| 4   | BTS3011TE recommended configurations1                                     | 12 |

| 4.1 | Pinout reminder                                                           | 12 |

| 4.2 | Analysis of possible configurations                                       | L3 |

| 5   | Appendix1                                                                 | 15 |

| 5.1 | BTF3xxxEJ STATUS pin diagram1                                             |    |

| 5.2 | BTS3011TE STATUS pin diagram1                                             |    |

| 6   | Revision history1                                                         | 17 |

2

# BTS3xxxEJ recommended configurations

## 2.1 Pinout reminder

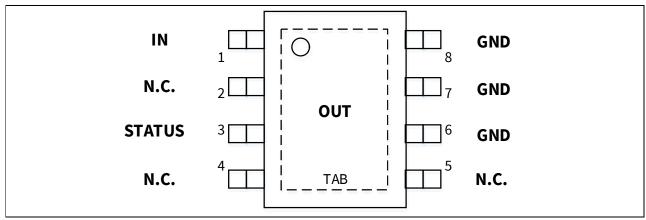

Figure 1 Pinout reminder

## Table 1Pin functionality reminder

| Pin            | Symbol   | I/O        | Function                                                            |

|----------------|----------|------------|---------------------------------------------------------------------|

|                |          | Input      | "high": switch ON the Power DMOS                                    |

| L L            | 1 IN     |            | "low": switch OFF the Power DMOS and reset the STATUS               |

| 2              | -        | -          | Not connected                                                       |

| 2              | 3 STATUS | Output     | "high": normal operation                                            |

| 3              |          | TUS Output | "low": overtemperature condition, stays low until reset             |

| 4              | -        | -          | Not connected                                                       |

| 5              | -        | -          | Not connected                                                       |

| 6,7,8          | GND      | I/O        | SOURCE of power DMOS and Logic, GND pins must be connected together |

| Cooling<br>tab | OUT      | I/O        | DRAIN of power DMOS. Connected to Load.                             |

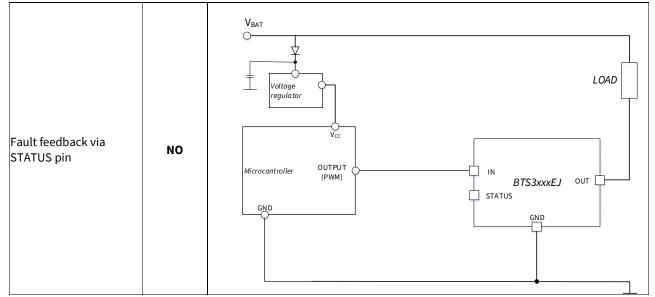

## 2.2 Analysis of possible configurations

Infineon HITFET<sup>™</sup> + BTS3xxxEJ family is easy to understand and straightforward to use.

If digital feedback is not needed in the application, then the STATUS pin can be left open with no drawback to BTS3xxxEJ family functionalities. It benefits from the smaller footprint of the TDSO-8 package compared to BTS3xxxTF the family.

Table 2 and Table 3 show an overview of the possible configurations.

$V_{BAT}$ 0-Ý LOAD Voltage regulator R<sub>STATUS</sub> Available, Vcc Fault feedback via reset by STATUS pin IN=low OUTPUT Microcontroller IN (PWM) оит 📋 BTS3xxxEJ INPUT STATUS (feed back) GND GND

Table 2 BTS3xxxEJ optimal configuration

#### Table 3 BTS3xxxEJ one-pin configuration

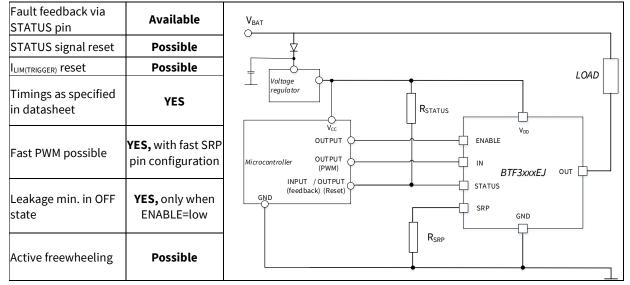

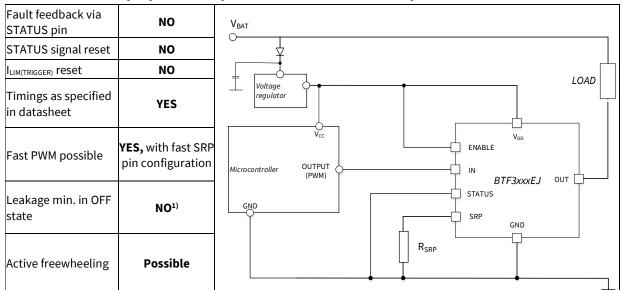

## 3 BTF3xxxEJ recommended configurations

The BTF3xxxEJ fully featured family offers attractive features in a TDSO-8 package. However, all features may not be needed in the application, or the pin count matters because of limited number of available microcontroller pins.

In this case, some of the pins may or may not be used, depending on the feature needed.

## 3.1 Quick find page

This section gives an overview of the features that can be shed depending on customer needs and the number of available pins from microcontroller.

Table 4 takes you to the configuration that you need and can help you save pins of your microcontroller.

For full feature configuration see **Table 6**.

#### Table 4 Application requirements

| No STATUS pin and no Fast PWM required                                         | Table 7  |

|--------------------------------------------------------------------------------|----------|

| I <sub>LIM(TRIGGER)</sub> is needed at each IN cycle and Slow PWM is enough*   | Table 8  |

| I <sub>LIM(TRIGGER)</sub> is needed at each IN cycle and Fast PWM is required* | Table 9  |

| No need for lowest leakage while OFF (ENABLE pin)                              | Table 10 |

| No STATUS, ILIM(TRIGGER) is needed at each IN cycle and Slow PWM is enough*    | Table 11 |

| No need for lowest leakage while OFF (ENABLE pin) and no need for STATUS pin   | Table 12 |

\* I<sub>LIM(TRIGGER)</sub> at each cycle may impact device lifetime. Refer to datasheet for values of I<sub>LIM(TRIGGER)</sub> and I<sub>LIM</sub> depending on your device. Refer to your local sales contact or distributor for more information.

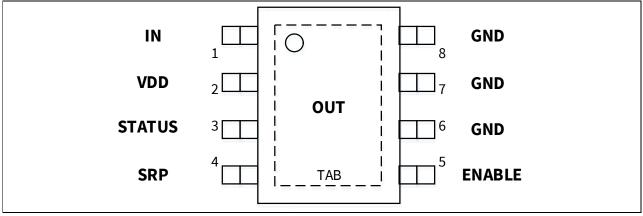

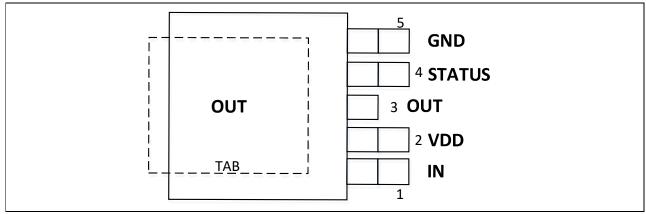

## 3.2 Pinout reminder

Figure 2 Pinout reminder

[There are several different "pinout reminder" sections and Figures. Add to each title what is specific about it for easy distinction.]

| Pin            | Symbol | I/O         | Function                                                            |

|----------------|--------|-------------|---------------------------------------------------------------------|

|                |        |             | "high": switch ON the Power DMOS                                    |

| 1              | IN     | Input       | "low": switch OFF the Power DMOS                                    |

|                |        |             | only if pin ENABLE is "high"                                        |

| 2              | VDD    | Input       | Logic supply voltage, 3 V to 5.5 V                                  |

|                | STATUS | Input       | Reset of latches by microcontroller pull-up                         |

| 3              |        | Output      | "high": normal operation                                            |

|                |        |             | "low": overtemperature condition                                    |

| 4              | SRP    | Input       | Slewrate control with external resistor                             |

|                |        |             | "high": IN pin enabled                                              |

| 5              | ENABLE | NABLE Input | "low" IN pin disabled;                                              |

|                |        |             | leakage currents are minimum                                        |

| 6,7,8          | GND    | I/O         | SOURCE of power DMOS and Logic, GND pins must be connected together |

| Cooling<br>tab | OUT    | I/O         | DRAIN of power DMOS. Connected to load.                             |

### Table 5Pin functionality reminder

# 3.3 Full feature configuration analysis – 3 pins available on microcontroller

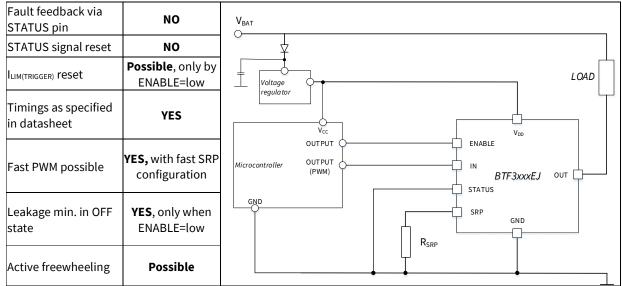

#### Table 6 Full feature configuration BTF3xxxEJ

## 3.4 Configurations when 2 pins from microcontroller available

#### Table 7 STATUS pin connected to GND

Go back to Error! Reference source not found. here.

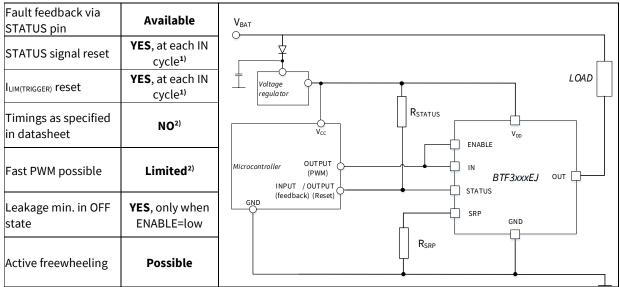

#### Table 8 IN pin and ENABLE pin connected together to microcontroller

- 1) Because IN pin and ENABLE pin are connected together, at each IN=ENABLE="low", STATUS and ILIM(TRIGGER) are reset.

- The turn-on is delayed at each cycle by t<sub>ENABLE(MASKING)</sub>. Refer to parameter in datasheet for more information.

The turn off each be capaid and as in fact SDD ain configuration.

The turn-off can be considered as in fast SRP pin configuration.

| Fault feedback via<br>STATUS pin     | NO                                          | V <sub>BAT</sub>                                                   |

|--------------------------------------|---------------------------------------------|--------------------------------------------------------------------|

| STATUS signal reset                  | Permanent <sup>1)</sup>                     | $\checkmark$ $\downarrow$                                          |

| ILIM(TRIGGER) reset                  | <b>YES</b> , at each IN cycle <sup>1)</sup> |                                                                    |

| Timings as specified<br>in datasheet | YES                                         | R <sub>1</sub>                                                     |

| Fast PWM possible                    | <b>YES,</b> with fast SRP pin configuration | Microcontroller OUTPUT O ENABLE<br>(PWM) IN BTF3xxxEJ OUT O STATUS |

| Leakage min. in OFF<br>state         | <b>YES</b> , only when<br>ENABLE=low        |                                                                    |

| Active freewheeling                  | Possible                                    |                                                                    |

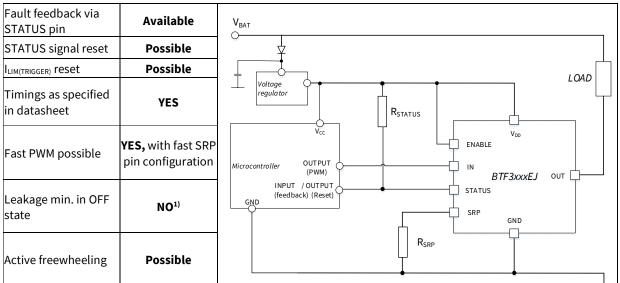

Table 9

STATUS pin permanently pulled-up to V<sub>DD</sub>

1) Reset by ENABLE= "low" is not applicable since STATUS is reset permanently and  $I_{LIM(TRIGGER)}$  is reset at each INPUT= "low" by the STATUS pin pulled-up to  $V_{DD}$  with the  $R_1$  resistor.  $R_1$ =220  $\Omega$  for  $V_{DD}$ =5 V and  $R_1$ =100  $\Omega$  for  $V_{DD}$ =3.3 V. See **Figure 4** for details on the STATUS pin structure.

Go back to Error! Reference source not found. here.

Table 10

ENABLE pin permanently connected to VDD

1) The leakage current on V<sub>DD</sub> pin is I<sub>DD(ON)</sub>. Refer to datasheet for values. It will not be acceptable in most automotive applications, where leakages in OFF state are critical, but can be accepted for non-automotive applications. The only advantage of this configuration over BTS3xxxEJ family is its fast PWM capability.

## 3.5 Configurations when only 1 pin from microcontroller is available

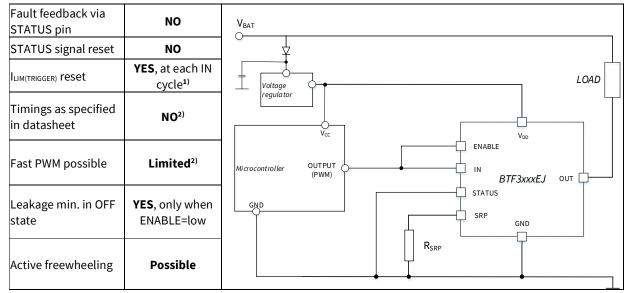

#### Table 11 IN pin and ENABLE pin connected together and STATUS pin connected to GND

- 1) Because IN pin and ENABLE pin are connected together, at each IN=ENABLE= "low", ILIM(TRIGGER) is reset.

- 2) The turn-on is delayed at each cycle by t<sub>ENABLE(MASKING)</sub>. Refer to parameter in datasheet for more information.

The turn-off can be considered as in fast SRP pin configuration.

#### Table 12ENABLE pin permanently connected to $V_{DD}$ and STATUS pin connected to GND

1) The leakage current on V<sub>DD</sub> pin is I<sub>DD(ON)</sub>. Refer to datasheet for values. It will not be acceptable in most automotive applications, where leakages in OFF state are critical, but can be accepted for non-automotive applications. The only advantage of this configuration over BTS3xxxEJ family is its fast PWM capability.

#### **BTS3011TE recommended configurations**

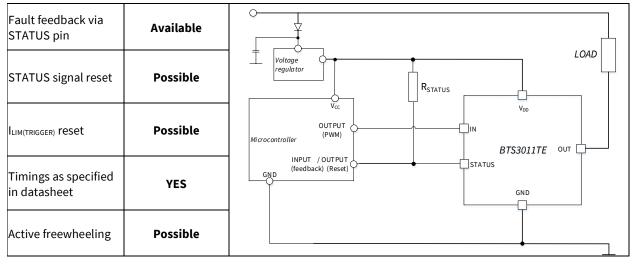

# 4 BTS3011TE recommended configurations

This chapter describes possible configurations for BTS3011TE.

## 4.1 Pinout reminder

Figure 3 Pinout reminder

#### Table 13Pin functionality reminder

| Pin     | Symbol | I/O         | Function                                    |

|---------|--------|-------------|---------------------------------------------|

|         |        | Input       | "high": switch ON the Power DMOS            |

| 1<br>1  | 1 IN   |             | "low": switch OFF the Power DMOS            |

| 2       | VDD    | Input       | Logic supply voltage, 3 V to 5.5 V          |

|         | STATUS | Input       | Reset of latches by microcontroller pull-up |

| 4       |        | ATUS Output | "high": normal operation                    |

|         |        |             | "low": overtemperature condition            |

| 5       | GND    | I/O         | SOURCE of power DMOS and Logic              |

| Cooling | Ουτ    | I/O         | DRAIN of power DMOS. Connected to Load.     |

| tab, 3  | 001    | 1,0         |                                             |

#### **BTS3011TE recommended configurations**

## 4.2 Analysis of possible configurations

#### Table 14Full feature configuration

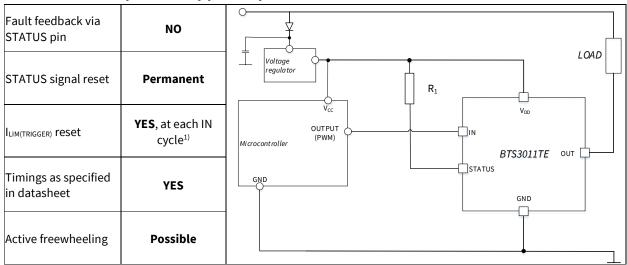

#### Table 15STATUS connected to GND

| Fault feedback via<br>STATUS pin     | NO               |                                                            |

|--------------------------------------|------------------|------------------------------------------------------------|

| STATUS signal reset                  | NO               | LOAD                                                       |

| Ilim(trigger) <b>reset</b>           | NO <sup>1)</sup> | Vcc<br>OUTPUT<br>Microcontroller<br>(PWM)<br>BTS3011TE OUT |

| Timings as specified<br>in datasheet | YES              | GND<br>GND<br>GND<br>GND<br>GND                            |

| Active freewheeling                  | Possible         |                                                            |

1) I<sub>LIM(TRIGGER)</sub> is available until first OT, then the current is limited to I<sub>LIM</sub>, until V<sub>DD</sub> is switched off and on again. Refer to datasheet for values.

#### **BTS3011TE recommended configurations**

1)  $I_{\text{LIM}(\text{TRIGGER})}$  at each cycle may impact device lifetime. Refer to datasheet for values of  $I_{\text{LIM}(\text{TRIGGER})}$  and  $I_{\text{LIM}}$ . Refer to your local sales contact or distributor for more information.  $R_1$ =600  $\Omega$  for  $V_{\text{DD}}$ =5 V and  $R_1$ =100  $\Omega$  for  $V_{\text{DD}}$ =3.3 V. See **Figure 5** for details on the STATUS pin structure. Refer to your local sales contact or distributor for more information.

Appendix

## 5 Appendix

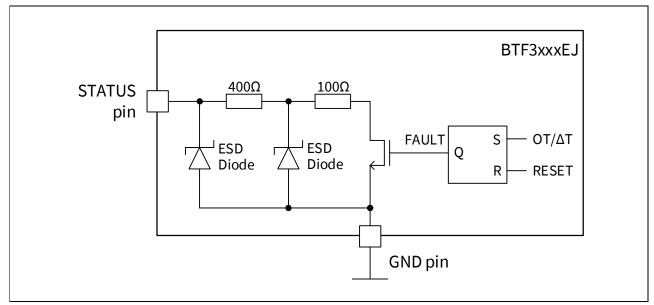

## 5.1 BTF3xxxEJ STATUS pin diagram

In order to keep STATUS and  $I_{LIM(TRIGGER)}$  permanently reset, the STATUS pin needs a pull-up resistor  $R_1$  to  $V_{DD}$  with a value different from the  $R_{STATUS}$  resistor. During an overtemperature (OT) event or a dynamic temperature ( $\Delta T$ ) event,  $R_1$  ensures that the voltage on the STATUS pin remains above the  $V_{STATUS(RESET)}$  threshold. Additionally, the STATUS pin must receive an  $I_{STATUS(RESET)}$  current as specified in order to provide sufficient current for reset. Refer to datasheet for values.

Figure 4 shows a schematic diagram of the internal structure of the STATUS pin for all HITFET<sup>™</sup> + BTF3xxxEJ. The values from the diagram can be used to compute the appropriate resistor-based customer's V<sub>DD</sub> voltage.

$R_1\!\!=\!\!220~\Omega$  can be used for  $V_{\text{DD}}\!\!=\!\!5~V$

$R_1\!\!=\!\!100\,\Omega$  can be used for  $V_{\text{DD}}\!\!=\!\!3.3\,V$

Figure 4 BTF3xxxEJ STATUS pin structure (typical values)

See BTF3xxxEJ recommended configurations.

Appendix

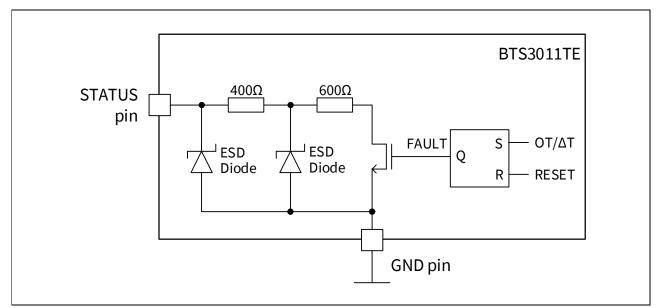

## 5.2 BTS3011TE STATUS pin diagram

In order to keep STATUS and  $I_{LIM(TRIGGER)}$  permanently reset, the STATUS pin needs a pull-up resistor  $R_1$  to  $V_{DD}$  with a value different from the  $R_{STATUS}$  resistor. During an overtemperature (OT) event or a dynamic temperature ( $\Delta T$ ) event,  $R_1$  ensures that the voltage on the STATUS pin remains above the  $V_{STATUS(RESET)}$  threshold. Additionally, the STATUS pin must receive an  $I_{STATUS(RESET)}$  current as specified in order to provide sufficient current for reset. Refer to datasheet for values.

Figure 5 shows a schematic diagram of the internal structure of the STATUS pin for HITFET<sup>™</sup> + BTS3011TE. The values from the diagram can be used to compute the appropriate resistor-based customer's V<sub>DD</sub> voltage.

$R_1$ =600 $\Omega$  can be used for  $V_{DD}$ =5V

$R_1\!\!=\!\!100\Omega$  can be used for  $V_{\text{DD}}\!\!=\!\!3.3V$

Figure 5 BTS3011TE STATUS pin structure (typical values)

See BTS3011TE recommended configurations.

**Revision history**

# 6 Revision history

Major changes since the last revision

| Revision Date Desc |            | Description of change                       |

|--------------------|------------|---------------------------------------------|

| Revision 1.1       | 2021-03-08 | Add Trade Mark on HITFET <sup>™</sup> words |

| Revision 1.0       | 2018-09-08 | Initial release                             |

#### **Trademarks of Infineon Technologies AG**

AURIX<sup>™</sup>, C166<sup>™</sup>, CanPAK<sup>™</sup>, CIPOS<sup>™</sup>, CoolGaN<sup>™</sup>, CoolMOS<sup>™</sup>, CoolSeT<sup>™</sup>, CoolSiC<sup>™</sup>, CORECONTROL<sup>™</sup>, CROSSAVE<sup>™</sup>, DAVE<sup>™</sup>, DI-POL<sup>™</sup>, DrBlade<sup>™</sup>, EasyPIM<sup>™</sup>, EconoBRIDGE<sup>™</sup>, EconoDUAL<sup>™</sup>, EconoPACK<sup>™</sup>, EconoPIM<sup>™</sup>, EiceDRIVER<sup>™</sup>, eupec<sup>™</sup>, FCOS<sup>™</sup>, HITFET<sup>™</sup>, HybridPACK<sup>™</sup>, Infineon<sup>™</sup>, ISOFACE<sup>™</sup>, IsoPACK<sup>™</sup>, i-Wafer<sup>™</sup>, MIPAQ<sup>™</sup>, ModSTACK<sup>™</sup>, my-d<sup>™</sup>, NovalithIC<sup>™</sup>, OmniTune<sup>™</sup>, OPTIGA<sup>™</sup>, OptiMOS<sup>™</sup>, ORIGA<sup>™</sup>, POWERCODE<sup>™</sup>, PRIMARION<sup>™</sup>, PrimePACK<sup>™</sup>, PrimeSTACK<sup>™</sup>, PROFET<sup>™</sup>, PRO-SIL<sup>™</sup>, RASIC<sup>™</sup>, REAL3<sup>™</sup>, ReverSave<sup>™</sup>, SatRIC<sup>™</sup>, SIEGET<sup>™</sup>, SIPMOS<sup>™</sup>, SmartLEWIS<sup>™</sup>, SOLID FLASH<sup>™</sup>, SPOC<sup>™</sup>, TEMPFET<sup>™</sup>, thinQ!<sup>™</sup>, TRENCHSTOP<sup>™</sup>, TriCore<sup>™</sup>.

Trademarks updated August 2015

#### **Other Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2021-03-08

**Published by**

Infineon Technologies AG

81726 Munich, Germany

© 2021 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

Document reference AppNote Number

#### IMPORTANT NOTICE

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of noninfringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contair dangerous substances. For information on the types in question please contact your nearest Infineor Technologies office.

Except as otherwise explicitly approved by Infineor Technologies in a written document signed by authorized representatives of Infineor Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof car reasonably be expected to result in personal injury.