### Overvoltage at the Buck Converter Output

## TLE6361 – Multi Voltage Processor Power Supply

Z8F52274257

## **Application Note**

Rev. 2.01, 2015-04-14

**Automotive Power**

### **Table of Contents**

|     | Table of Contents                                                  |

|-----|--------------------------------------------------------------------|

| 1   | Abstract 3                                                         |

| 2   | Detailed problem description                                       |

| 2.1 | Relevant TLE6361 operation principle                               |

| 2.2 | Buck regulator control failure at bouncing battery                 |

| 2.3 | Buck regulator control failure at SPI turn-off command             |

| 2.4 | Buck regulator control failure due to disturbances at the FB input |

| 3   | Proposed solutions                                                 |

| 3.1 | Workaround circuit for bouncing battery                            |

| 3.2 | Solution to avoid overshoot at SPI turn-off commands               |

| 3.3 | Layout recommendation to avoid noise induced failure               |

| 3.4 | Additional patch proposal1                                         |

| 4   | Final solution 12                                                  |

| 5   | Revision History 13                                                |

#### **Abstract**

### 1 Abstract

During application tests a certain case of failure may be observed with the TLE6361: the increase of the Buck converter output voltage up to battery voltage levels resulting in damage of the device.

This Application note is intended to provide some details on the failure mechanisms and show workaround solutions to avoid destruction, by proper operation of the TLE6361.

**Detailed problem description**

### 2 Detailed problem description

### 2.1 Relevant TLE6361 operation principle

In order to understand the failure in detail a brief explanation of the TLE6361's operation principle is necessary.

The internal circuit blocks that need to be considered for this failure are the internal biasing and wake up block, the Buck converter control block, the gate driver supply block and the external charge pump block.

Internal biasing, e.g. the reference and the logic supply, as well as the step down control block are supplied in the TLE6361 from two sides, the battery line (IN pins) and the Buck converter output line (FB pins). In order to guarantee the supply of the internal circuit blocks as long as possible, even at low input voltage, the battery line and the Buck converter output line are tied together in an OR function on IC level.

The internal biasing and logic blocks are enabled and disabled by the internal wake up block. The wake up block itself has two inputs, the Wake pin and the sleep-bit in the SPI. In order to activate the TLE6361, a signal level above the wake up threshold has to be applied to the Wake pin. For device shutdown, the appropriate bit in the SPI has to be set by the micro controller and the Wake signal must be below the wake up threshold. A simple low signal at the Wake pin only will not turn off the device, which means if the micro controller is not powered the TLE6361 cannot be shut down without disconnecting the battery supply voltage.

The gate driver supply is generated under normal operation (except at start-up) by the help of the external charge pump circuit, i.e. the bootstrap capacitor providing the charge to enhance the internal DMOS is powered from this external charge pump circuit. The charge pump itself operates from the Buck output voltage rail, which means it operates independent from the input voltage. This means that once the output of the Buck converter has powered up, the charge pump is operating and able to provide the gate driver supply even if the input voltage had decreased to zero again. The gate driver supply, i.e. the bootstrap capacitor, is discharged only by powering the gate of the DMOS stages and leakage currents. The bootstrap capacitor is not discharged actively at device turn off.

#### 2.2 Buck regulator control failure at bouncing battery

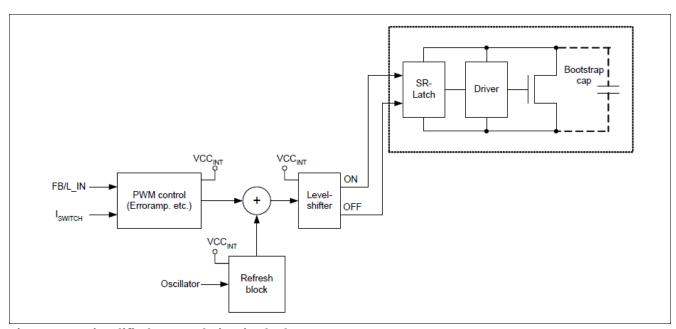

The main simplified blocks of the Buck control loop, which are relevant for this failure are shown below in **Figure 1**. The PWM signal to drive the power DMOS is generated in the current mode control block with inputs "Buck output voltage, FB/L\_IN" and "main switch current,  $I_{SWITCH}$ ". In addition to the control block, there is also a refresh block in order to reset (i.e. turn off) the main switch in case the Buck control loop fails. The refresh signal is generated with a delay of eight clock cycles after a loop failure.

#### **Detailed problem description**

Figure 1 Simplified Internal Circuit Blocks

The level shifter transforms the logic signals generated by the PWM control and the refresh logic to the high side driver block, which includes the latch and the driver for the Power DMOS stages itself. The high side driver block is moving up and down according to the Bootstrap supply voltage independent from the internal 5V VCC logic supply voltage which is biasing the PWM and Refresh block.

Now if the input voltage collapses, the Buck converter output voltage decreases as well. The control loop assumes low battery and sets the latch in the high side driver block, which means the main switch is completely turned on. Even when the voltages at the input and at the Buck output are too low to supply the logic blocks PWM and Refresh, the latch is still set and the DMOS is still on (remember that the gate driver supply block is supplied by the bootstrap capacitor and the external charge pump).

If the battery decreases down to zero and stays there, the Buck output voltage would also decrease to zero, disabling the external charge pump. With the disabled charge pump, the Bootstrap voltage will not be maintained so the main switch will also be turned off. To power up the device again, the battery voltage must increase to about 7V and the Wake signal has to be above the wake up threshold.

During TLE6361's control loop failure the scenario is as follows. The input voltage at the device is swinging, not staying long enough at the low level in order to allow the Bootstrap capacitor to discharge. The internal logic supply cannot be established immediately with the battery recovery because of internal delays caused by the power up procedure of the internal supply. Due to this fact, the PWM logic and Refresh logic are not supplied, therefore, they cannot send a turn off command to the driver circuitry. The main switch of the Buck converter stays on 100% allowing the Buck output voltage to follow the input voltage. This error condition will persist until the PWM/ Refresh logic supply is established. The worst case, i.e. the highest possible output voltage occurs, when the refresh circuit has to reset the power switch. Measurements on ceramic samples have shown delays (or loop "dead times") up to 50µs.

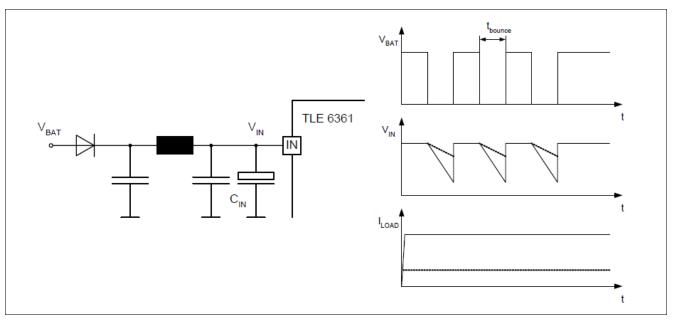

Note: In applications the failure of the TLE6361 described above is most likely to happen only with low input capacitor configuration. The diagram below shows a typical input configuration of the input line on the TLE6361. At the module input, there's the reverse polarity protection followed by the input Pi-filter with storage caps at the input pins of the TLE6361. In the timing diagrams voltages with bouncing are shown for various load currents at the battery and at the input of the device.

#### **Detailed problem description**

Figure 2 Input Configuration and Timing

The voltage at the input of the TLE6361 (which acts as the supply line for the internal blocks) can be approximated to:

(2.1)

$$V_{IN} = V_{BAT} - \left(I_{LOAD} \cdot \frac{t_{bounce}}{C_{IN}}\right)$$

As long as the input voltage at the TLE6361 does not decrease below 5V, the failure described above can never happen, because the internal blocks are still supplied. For example, with a battery voltage of 13.5V, a bouncing time of 300µs, an input capacitor configuration of 47µF and a load current at the Buck converter of 1A a minimum battery voltage at the input of roughly 7.1V would be obtained, without a failure of the device. Another component helping to avoid destruction after the control loop's black out during low battery is the Buck output inductance. Applications using inductors with high saturation currents can overcome the "dead time". The Buck output cannot follow the input immediately due to the inductance-effect, which is given still at high (and increasing) currents. With the control loop taking over again, i.e. turning off the main switch, a non destructive overshoot at the output is recognized. However the choice of the inductor cannot prevent the primary failure, i.e. the control loop's failure.

### 2.3 Buck regulator control failure at SPI turn-off command

Another situation which may cause the Buck regulator output voltage to exceed maximum ratings can occur when the Boost pin is connected directly to the input (battery line) and a SPI turn off command is sent at hot temperature.

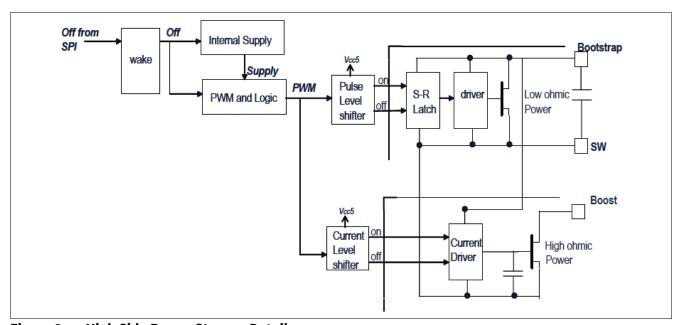

As described in the data sheet, the high side power switch consists of two power stages, a low ohmic main power stage and a higher ohmic secondary stage. This two-power DMOS approach was chosen to improve the switching behavior (EME) of the high side stage. Each of the two high side switching blocks contains its own level shifter which receives the signals from the Buck converter control loop to turn on and off the individual

Application Note 6 Rev. 2.01, 2015-04-14

#### **Detailed problem description**

power stage. Both high side blocks are supplied from the same high side driver supply, the Bootstrap capacitor. A more detailed block diagram is shown in **Figure 3**.

It is recognized that the high ohmic driver block is simpler than the main power stage as the high ohmic power stage was intended to be connected to the Buck output. (See data sheet, application diagram: the Boost pin is connected to the Buck output by a diode configuration).

Figure 3 High Side Power Stages - Detail

The SPI turn off command disables the internal logic supply Vcc5 as well as it resets the Buck converter control block. As soon as the Buck converter control block receives the turn off command from the SPI, it sends the off command to the level shifters of the two high side switches. Due to signal delay times it can happen that the level shifter of the high ohmic power DMOS receives the turn off command too late, i.e. when its supply voltage Vcc5 had collapsed already. Not being supplied, the high ohmic power stage's level shifter is not able to transfer the off command to the switch, which means in case the high ohmic power stage was turned on it will not be turned off and the output can reach battery voltage level.

### 2.4 Buck regulator control failure due to disturbances at the FB input

In applications where the Buck converter output isn't fed back to the TLE6361 FB/L\_IN pin exclusively but is used to supply other circuits on the PCB, the Buck converter overvoltage failure could potentially be observed. It is recognized that high frequency noise on the FB/L\_IN pin induced by e.g. other switching elements on the board can mislead the internal Buck control loop. The main switch is turned on permanently causing overshoot at the Buck converter output.

Once the Buck converter switch is turned on by noise, the reset / turn off of this main switch is forced only by the refresh block within the Buck control loop (compare **Figure 1**). At high input voltage / low buck inductance configured systems the failure is more likely to happen because the refresh cycle is too long to avoid overvoltage at the Buck output.

In **Section 3.3** some guidelines are given for proper layout in order to avoid disturbance at the FB/L\_IN input of the TLE6361.

**Proposed solutions**

### 3 Proposed solutions

### 3.1 Workaround circuit for bouncing battery

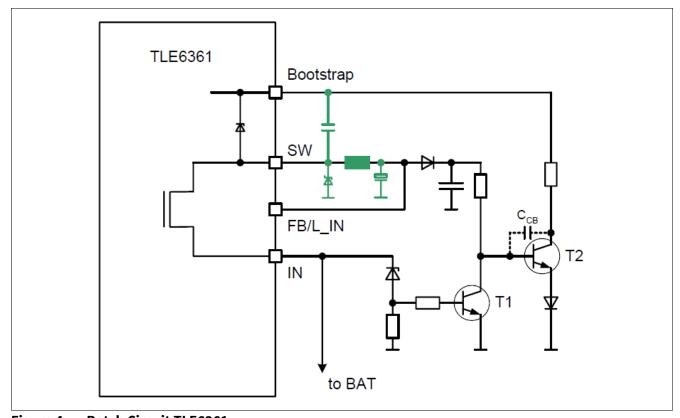

In order to prevent failure of the Buck converter output voltage, the following workaround circuit in **Figure 4** is suggested. The main purpose of this circuitry is to discharge the gate driver supply, (i.e. the bootstrap capacitor) dependent on the input voltage in order to avoid voltage overshoot at the output.

**Figure 4** shows a possible solution on how to discharge the bootstrap capacitor.

Figure 4 Patch Circuit TLE6361

With undervoltage condition at the input pin (i.e. battery voltage lower than the Zener voltage), the base of T1 is kept low and the base of T2 is set to the Buck converter output voltage level, which enables T2 and discharges the Bootstrap capacitor.

In order to discharge the Bootstrap capacitor without destroying the internal ESD protection diode between the Bootstrap and the SW pins, (which would cause a permanent short between SW and Bootstrap), if the SW pin is not GND level when discharging, the discharge current has to be limited to about 20mA max. by a resistor. The maximum voltage at the bootstrap pin to calculate the resistor value is obtained by adding the maximum bootstrap voltage (10.5V) to the maximum battery voltage.

The diode from the emitter of T2 to GND avoids unwanted turn on of T2 (which is the discharge of the bootstrap capacitor) at high temperatures when the saturation voltage of T1 is close to the base emitter enable voltage of T2.

Care has to be taken when selecting transistor T2 in terms of its parasitic collector-base coupling capacitance (marked as  $C_{CB}$  in **Figure 4**). As the collector voltage of T2 is moving up and down with the voltage at the

#### **Proposed solutions**

bootstrap pin, the base might be affected through this coupling capacitance to turn on T2. Therefore, low parasitic coupling capacitor values are preferred.

The diode at the output of the Buck converter is for decoupling and the resistor to the base of T2/collector of T1 is to limit the current through T1 during normal battery operation.

#### 3.2 Solution to avoid overshoot at SPI turn-off commands

To overcome the risk that SPI turn off commands may not turn off the high ohmic power stage and cause voltage overshoot at the Buck output, it is **recommended that the Boost pin is left open** when the usage intended was connecting it to battery directly. When the Boost pin is fed from the output by the diode and capacitor configuration as recommended in the data sheet, a disconnection of this pin is not necessary, no overshoot can occur in this case.

### 3.3 Layout recommendation to avoid noise induced failure

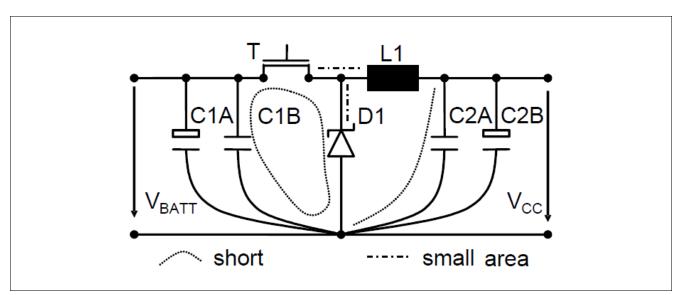

When considering the layout of a Buck converter circuit, some general guidelines have to be taken into consideration. **Figure 5** shows a simplified example of the components used for Buck converter circuits: input capacitors, switch, catch diode, Buck inductance and output capacitors.

Figure 5 Main Components in a Buck Converter Circuit

Referring to **Figure 5** the following guidelines should be considered:

- The loop containing C1B, T and D1, where currents with high di/dt occur should be as small as possible (or as low inductive as possible) to avoid interfering voltages.

- The connection between T, D1 and L1 where high dv/dt occurs should be as short as possible (or as low capacitive as possible, small area).

- C1A, C1B, C2A and C2B have to be connected by short lines (low inductive) to be effective in the high frequency range.

- To guide high frequency current: The strip lines from V<sub>BATT</sub> should pass the pins of C1A and C1B before

connecting the switch. The same applies to the output of the Buck inductance for C2A and C2B before

reaching V<sub>CC</sub>.

- The application circuit should have a ground plane below it on the other side of the PCB.

#### **Proposed solutions**

- On the top layer, there should be a star type of GND connection which then goes to the GND layer. Connecting input capacitors, output capacitors and the catch diode at one point avoids large high-frequency currents on the GND plane.

- The GND pins of TLE6361 should be connected directly to the GND plane.

- The GND plane below the Buck application circuit should also be "star"-connected to the GND connectors of other networks.

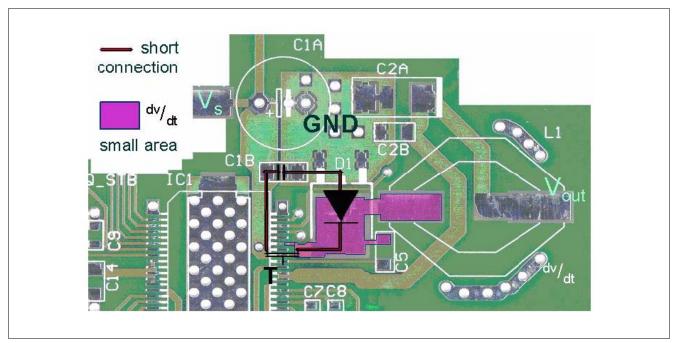

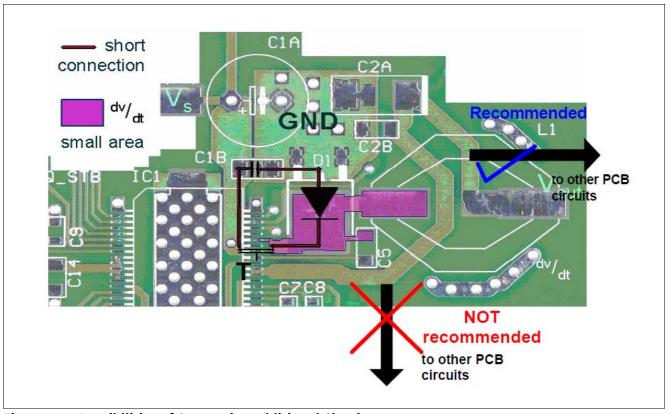

An example for those recommendations above is given in **Figure 6**. It is recognized that the loop consisting of C1s, T and D1 is as small as possible, also the area connecting T, D1 and L1. The strip lines are guided from battery to C1s - T - D1 - L1 - C2s and finally back to the feedback input of the IC. The bottom side of the PCB is the GND plane.

Figure 6 Layout Example TLE6361

When feeding additional potentially noisy circuitry on the PCB (others than just the FB/ L\_IN input of the TLE6361) from the Buck regulator output, it should be avoided to tap off this Buck supply line at the FB/L\_IN pin. The capacitors located at the Buck converter output would not filter the signals, i.e. noise coming in from this supply line into the FB/L\_IN pin.

**Figure 7** below shows the layout with two examples of connecting additional circuitry. When feeding the additional circuitry close to the control loop feedback input, behind the filter capacitors C2A and C2B, the line to the IC is not filtered. Therefore noise can enter the IC and disturb the system. Tapping off the Buck output rail just at the Buck inductance ensures proper noise filtering of the output capacitors C2A and C2B, the control loop of the IC is not influenced.

Application Note 10 Rev. 2.01, 2015-04-14

#### **Proposed solutions**

Figure 7 Possibilities of Connecting additional Circuitry

### 3.4 Additional patch proposal

The solutions in the previous sections discuss preventive measures for avoiding excessive Buck output voltage.

However, there is also the possibility to create a patch circuit which reacts to the failure itself by monitoring the Buck output voltage. In case the Buck output voltage starts to increase to unallowed values, the patch must quickly discharge the Bootstrap capacitor (by shortening the Bootstrap pin to the SW pins, e.g. with a PMOS transistor). Due to undervoltage at the Bootstrap the main switch is turned off and the Buck output voltage cannot increase further.

**Final solution**

### 4 Final solution

In order to fix the failing behavior of the Buck control loop a redesign is performed on the TLE6361. The redesign will include an undervoltage detection circuit, an improved refresh block and an additional current limit shutdown circuit in the high side driver blocks.

**Revision History**

### **5** Revision History

| Revision | Date       | Changes                                            |

|----------|------------|----------------------------------------------------|

| 1.32     | 2015-04-08 | Infineon Style Guide update.<br>Editorial changes. |

#### **Trademarks of Infineon Technologies AG**

AURIXTM, C166TM, Canpaktm, CIPOSTM, CIPURSETM, CoolGantm, CoolMostm, CoolSictm, CoolSictm, Corecontroltm, Crossavetm, Davetm, Di-Poltm, Drbladetm, EasyPIMTM, EconoBRIDGETM, EconoDUALTM, EconoPACKTM, EconoPIMTM, EiceDRIVERTM, eupectm, FCOSTM, HITFETTM, HybridPACKTM, ISOFACETM, IsoPACKTM, I-Wafertm, MIPAQTM, ModSTACKTM, my-dtm, NovalithIctm, OmniTunetm, OPTIGATM, OptiMostm, ORIGATM, POWERCODETM, PRIMARIONTM, PrimePACKTM, PrimeSTACKTM, PROFETTM, PRO-SILTM, RASICTM, REAL3TM, ReverSavetm, Satrictm, SIEGETTM, SIPMOSTM, SmartLewistm, Solid Flashtm, SPOCTM, TEMPFETTM, thinQ!TM, TRENCHSTOPTM, TriCoretm.

#### Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. ANSI™ of American National Standards Institute. AUTOSAR™ of AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. HYPERTERMINAL™ of Hilgraeve Incorporated. MCS™ of Intel Corp. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ of Openwave Systems Inc. RED HAT™ of Red Hat, Inc. RFMD™ of RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Trademarks Update 2014-07-17

#### www.infineon.com

Edition 2015-04-14 Published by Infineon Technologies AG 81726 Munich, Germany

© 2014 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

Document reference Doc\_Number

#### **Legal Disclaimer**

THE INFORMATION GIVEN IN THIS APPLICATION NOTE (INCLUDING BUT NOT LIMITED TO CONTENTS OF REFERENCED WEBSITES) IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE INFINEON TECHNOLOGIES COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE INFINEON TECHNOLOGIES COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE REAL APPLICATION. INFINEON TECHNOLOGIES HEREBY DISCLAIMS ANY AND ALL WARRANTIES AND LIABILITIES OF ANY KIND (INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Office. Technologies Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.