## **Reference Manual**

# iMOTION™ Motor Control IC integrating the Motion Control Engine (MCE) with a Microcontroller

### **Quality Requirement Category: Industry**

#### **Features**

- Motion Control Engine (MCE) with 100MHz

Field proven computation engine for high efficiency sinusoidal sensor less motor control

- o Ready-to-use solution for high efficiency variable speed drives

- Sensor less field oriented control (FOC) of permanent magnet synchronous motors (PMSM)

- o Built-in support for single or two shunt current feedback

- Integrated protection features

- MCU: 8051 with 30MHz

- Built-in digital & analog peripherals: oscillator, A/D converter, OP amps & comparators

- UART & I2C serial interfaces

- Multiple additional analog & digital application IOs

- o JTAG interface

- Up to 64 KB flash or 32 KB OTP memory

- Packages from tiny 5x5mm<sup>2</sup> QFN-32 to QFP64

## **Applications**

- Home appliances

- Pumps & fans

- Servo drives (IRMCx143)

- Any other PMSM drive

## **Description**

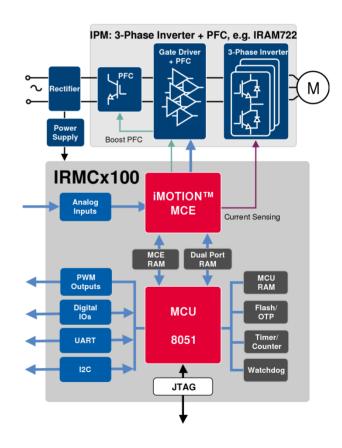

The IRMCx100 series combines the iMOTION™ motion control engine (MCE) with an additional microcontroller (MCU) to improve application flexibility. The MCE does not require algorithm programming and can be combined with a µIPM™ or a discrete power stage for FOC control of a PMSM.

The industry standard 8051 MCU can be programmed by the customer to control the MCE and to implement additional functionality running almost independently from the motion control algorithm on the MCE.

March 25, 2015 Version 2.4

International

Rectifier

## TABLE OF CONTENTS

| 1. Overview     |                                                             | 10 |

|-----------------|-------------------------------------------------------------|----|

| 1.1 System C    | omponents                                                   | 12 |

| 1.2 Memory I    | Resources                                                   | 13 |

| 1.2.1 OTP       | Memory (IRMCK1xx)                                           | 13 |

| 1.2.2 Flash     | h Memory (IRMCF1xx)                                         | 13 |

| 1.2.3 Data      | RAM                                                         | 13 |

| 1.3 Byte Orde   | ering                                                       | 14 |

| 1.4 Reset Med   | chanism and Boot Process                                    | 14 |

| 2 8051 Microcor | ntroller                                                    | 18 |

| 2.1 Instruction | n Set                                                       | 18 |

| 2.2 Special Fu  | unction Registers                                           | 22 |

| 2.3 Periphera   | l Registers                                                 | 24 |

| 2.4 General F   | Functions                                                   | 26 |

|                 | essor Registers                                             |    |

| 2.4.2 Gene      | eral Purpose I/O                                            | 28 |

| 2.4.3 Cloc      | k Selection and PLL Frequency Configuration                 | 34 |

|                 | LL Setup Register for IRMCK1xx                              |    |

| 2.4.3.2 PI      | LL Setup Register for IRMCF1xx                              | 36 |

| 2.4.3.3 Bo      | oot Clock Operation                                         | 39 |

| 2.4.4 Sleep     | p Mode Function                                             | 39 |

| 2.4.4.1 Slo     | eep Mode for IRMCK1xx                                       | 39 |

| 2.4.4.2 Slo     | eep Mode for IRMCF1xx                                       | 40 |

| 2.4.5 Misc      | cellaneous Functions                                        | 40 |

|                 |                                                             |    |

|                 | dard Interrupts                                             |    |

| 2.5.2 Exter     | nded Interrupts                                             | 44 |

|                 | oling Interrupts                                            | 44 |

|                 | rupt Priority                                               |    |

|                 | ice Order                                                   |    |

|                 | rupt Latency                                                |    |

|                 | rupt Vectors                                                |    |

|                 |                                                             |    |

|                 | er Prescaler                                                |    |

|                 | eral-Purpose Timer/Counters                                 |    |

|                 | odes of Operation                                           |    |

|                 | onfiguring the Timers                                       |    |

|                 | sing the Timers to Measure a Time Interval                  |    |

|                 | sing the Timers to Signal when a Defined Period has Elapsed |    |

|                 | sing the Timers as Event Counters                           |    |

|                 | eading the Timers                                           |    |

|                 | chdog Timer                                                 |    |

|                 | ure Timer                                                   |    |

|                 | E Pin Timers                                                |    |

|                 |                                                             |    |

|                 | M                                                           |    |

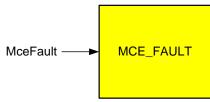

|                 | Serial Interface                                            |    |

|                 | mand Descriptions for the I <sup>2</sup> C Interface        |    |

|                 | evice Address                                               |    |

|                 | ead and Write Commands                                      |    |

|                 | mand Descriptions for the SPI Interface                     |    |

|                 | ead Instructions                                            |    |

|                 | rite Instructions                                           |    |

| 3 Motion Contro | ol Engine                                                   | 68 |

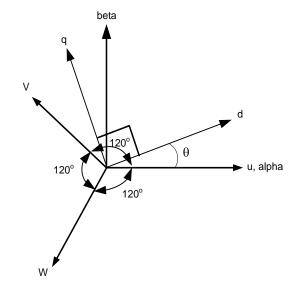

|       | Cotating Frame Notation and Conventions          |       |

|-------|--------------------------------------------------|-------|

| 3.2.1 | Frequency Domain Blocks                          |       |

| 3.2.1 | ± • •                                            |       |

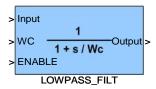

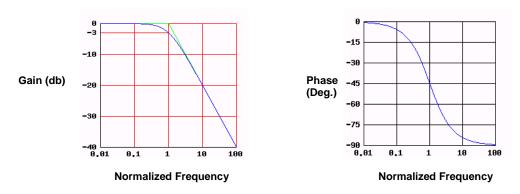

|       | 1.2 LOWPASS_FILT – First Order Low Pass Filter   |       |

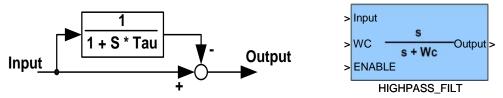

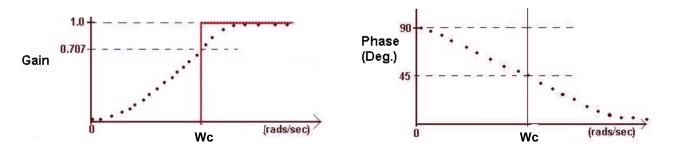

|       | 1.3 HIGHPASS_FILT – First Order High Pass Filter |       |

| 3.2.2 | Coordinate Transformation Blocks                 |       |

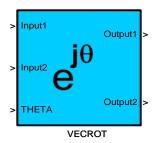

| 3.2.2 |                                                  |       |

|       | 2.2 CLARK – Inverse Clark Transformation         |       |

| 3.2.3 | Utility Blocks                                   |       |

| 3.2.3 | •                                                |       |

| 3.2.  |                                                  |       |

| 3.2.  | 1                                                |       |

| 3.2.  | · · · · · · · · · · · · · · · · · · ·            |       |

| 3.2.  |                                                  |       |

| 3.2.  |                                                  |       |

| 3.2.  |                                                  |       |

| 3.2.  |                                                  |       |

| 3.2   |                                                  |       |

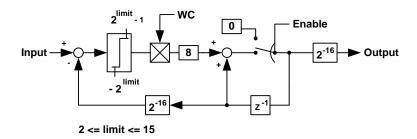

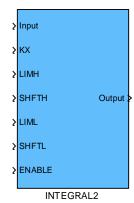

|       | 3.10 INTEGRAL2 – Integral with Limit             |       |

| 3.2.4 | Math                                             |       |

| 3.2.4 |                                                  |       |

| 3.2.  |                                                  |       |

| 3.2.  |                                                  |       |

| 3.2.  |                                                  |       |

| 3.2.  |                                                  |       |

| 3.2.  |                                                  |       |

| 3.2.  |                                                  |       |

| 3.2.  |                                                  |       |

| 3.2.  |                                                  |       |

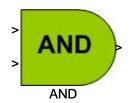

|       | 4.10 AND – Bitwise Logical AND                   |       |

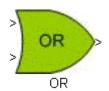

|       | 4.11 OR – Bitwise Logical OR                     |       |

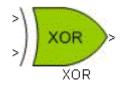

|       | 4.12 XOR – Bitwise Logical Exclusive OR          |       |

|       | Aotion Peripherals                               |       |

| 3.3.1 | SENSORLESS FOC                                   |       |

| 3.3.1 | <del>-</del>                                     |       |

| 3.3.  |                                                  |       |

| 3.3.  |                                                  |       |

| 3.3.  | 1                                                |       |

| 3.3.  |                                                  |       |

| 3.3.  | •                                                |       |

| 3.3.2 | CURRENT_MEAS                                     |       |

| 3.3.2 |                                                  |       |

| 3.3.3 | DC_BUS_VOLTAGE                                   |       |

| 3.3.4 | A_D – A/D Converter and A/D Compensation         |       |

| 3.3.4 | _                                                |       |

| 3.3.  |                                                  |       |

| 3.3.4 |                                                  |       |

| 3.3.4 |                                                  |       |

| 3.3.5 | Low Loss Space Vector PWM                        |       |

| 3.3.3 | •                                                |       |

| 3.3.  |                                                  |       |

| 3.3.  |                                                  |       |

| 3.3.  |                                                  |       |

| 3.3.  |                                                  |       |

| ٠.٠.  | VIC OMERIII                                      | , 120 |

| 3.3.6    | FAULTS Block                                     |     |

|----------|--------------------------------------------------|-----|

| 3.3.6    | .1 Fault State Control                           | 132 |

| 3.3.7    | MCE_FAULT Generator                              | 133 |

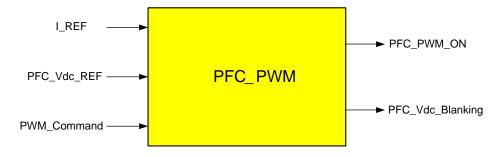

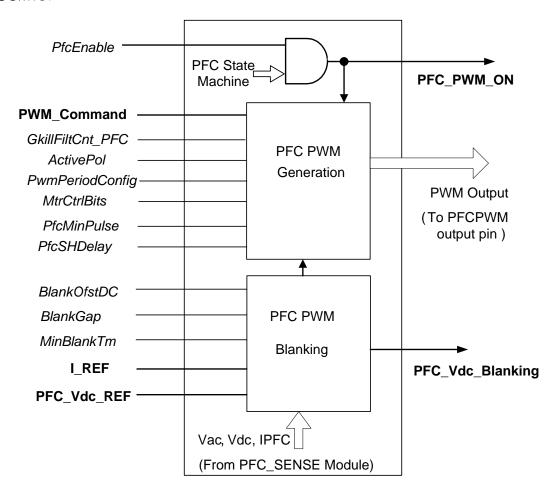

| 3.3.8    | PFC_PWM                                          | 133 |

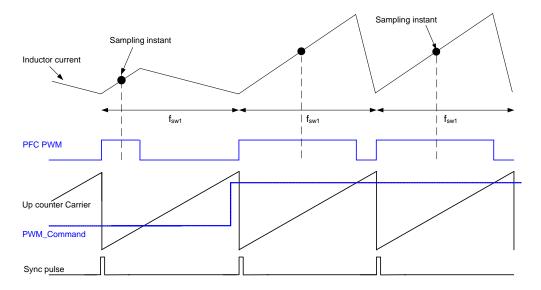

| 3.3.8    | .1 PFC PWM Generation                            | 135 |

| 3.3.8    | .2 PFC PWM Blanking                              | 136 |

| 3.3.9    | PFC_SENSE                                        | 137 |

| 3.3.10   | PFC_AC_STATUS                                    | 138 |

| 3.3.11   | PFC_MOTOR_MISC                                   | 139 |

| 3.4 Me   | otion Peripheral Registers                       | 140 |

| 3.4.1    | System Write Register Group                      | 141 |

| 3.4.2    | PWM Configuration Write Register Group           | 145 |

| 3.4.3    | Torque Loop Configuration Write Register Group   | 149 |

| 3.4.4    | Velocity Control Write Register Group            |     |

| 3.4.5    | Closed Loop Angle Estimator Write Register Group |     |

| 3.4.6    | Open Loop Angle Estimator Write Register Group   |     |

| 3.4.7    | Startup Angle Estimator Write Register Group     |     |

| 3.4.8    | Phase Loss Detect Write Register Group           |     |

| 3.4.9    | Current feedback Write Register Group            |     |

| 3.4.10   | Catch Spin Write Register Group                  |     |

| 3.4.11   | User Control Write Register Group                |     |

| 3.4.12   | Field Weakening Control Write Register Group     |     |

| 3.4.13   | Protection Write Register Group                  |     |

| 3.4.14   | External Signals Write Register Group            |     |

| 3.4.15   | AD Correction Write Register Group               |     |

| 3.4.16   | Miscellaneous Signals Write Register Group       |     |

| 3.4.17   | PFC Control Write Register Group                 |     |

| 3.4.18   | System Read Register Group                       |     |

| 3.4.19   | System Status Read Register Group                |     |

| 3.4.20   | DC Bus Voltage Read Register Group               |     |

| 3.4.21   | FOC Diagnostic Data Read Register Group          |     |

| 3.4.22   | Velocity Status Read Register Group              |     |

| 3.4.23   | Current Feedback Offset Read Register Group      |     |

| 3.4.24   | Protection Read Register Group                   |     |

| 3.4.25   | AD Correction Read Register Group                |     |

| 3.4.26   | PFC Status Read Register Group                   |     |

| 4 8051/1 | MCE Interface                                    |     |

|          | emory Map                                        |     |

|          | MCK1xx OTP Memory                                |     |

|          | MCF1xx Flash Memory                              |     |

|          | ne Shared Data RAM                               |     |

| 4.4.1    | Reading and Writing Shared RAM                   |     |

| 4.4.2    | Arbitration                                      |     |

| 4.5 M    | CE Processor Registers                           |     |

|          | terrupts from the MCE to the 8051                |     |

| 4.6.1    | MCE Interrupt                                    |     |

| 4.6.2    | SYNC Interrupt                                   |     |

| 4.6.3    | Fault Interrupt                                  |     |

|          | CE Development Process                           |     |

|          | CE Design Generation                             |     |

|          | eating an MCE Design Using Simulink              |     |

|          | mulink MCE Design Components                     |     |

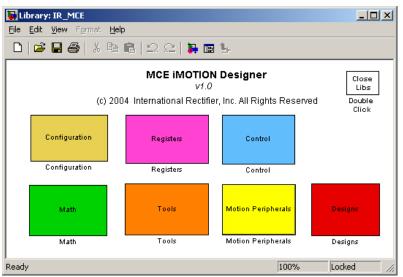

| 5.3.1    | The MCE Library                                  |     |

| 5.3.1    | ·                                                |     |

| 5.3.1    | <u> </u>                                         |     |

|          |                                                  |     |

|   | 5.3.1.3    | Control                                            | 210 |

|---|------------|----------------------------------------------------|-----|

|   | 5.3.1.4    | Math                                               | 210 |

|   | 5.3.1.5    | Tools                                              | 210 |

|   | 5.3.1.6    | Motion Peripherals                                 |     |

|   | 5.3.1.7    | Designs                                            |     |

|   | 5.3.2 S    | tandard Simulink Library Components                |     |

|   | 5.3.2.1    | Enabled Subsystem                                  |     |

|   | 5.3.2.2    | Constant                                           | 211 |

|   | 5.3.2.3    | Scope                                              | 211 |

|   | 5.3.2.4    | Goto and From                                      |     |

|   | 5.3.2.5    | Unit Delay                                         | 211 |

|   | 5.4 The M  | ICE Compiler                                       | 212 |

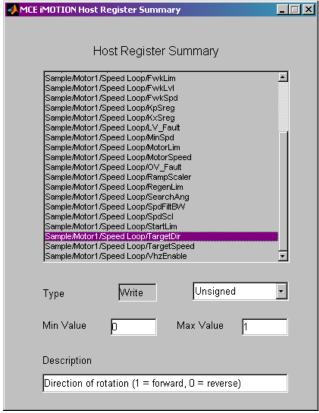

|   | 5.5 The H  | ost Register Summary Utility                       | 214 |

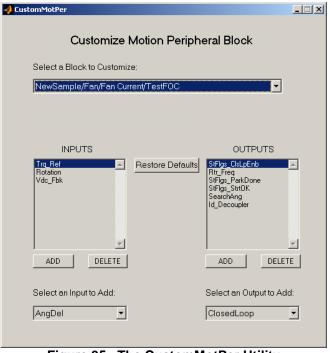

|   | 5.6 Custon | mizing Motion Peripheral Library Blocks            | 215 |

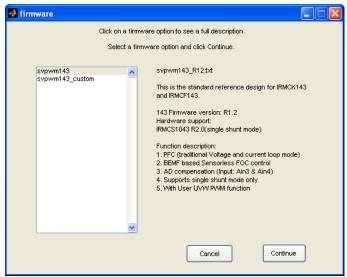

|   |            | ling Information about Compatible Firmware Options |     |

|   | 5.8 MCE    | Design Hierarchical Format                         | 218 |

| 6 | The 8051 Γ | Development Process                                | 221 |

|   | 6.1 The K  | eil and FS2 Tools                                  | 221 |

|   |            | oftware Installation                               |     |

|   |            | The Keil Compiler                                  |     |

|   | 6.1.3 D    | Debugging                                          | 222 |

|   |            |                                                    |     |

## LIST OF FIGURES

| Figure 1. Typical Two Shunt Leg Current Sensing Application Diagram Using IRMCx100  |     |

|-------------------------------------------------------------------------------------|-----|

| Figure 2. Typical Application of IRMCx188 with Single Shunt Current Sensing and PFC | 11  |

| Figure 3. IRMCK171 Internal Block Diagram                                           |     |

| Figure 4. IRMCK143 Internal Block Diagram                                           | 12  |

| Figure 5. Reset Module                                                              | 15  |

| Figure 6. Reset and Boot Process                                                    | 16  |

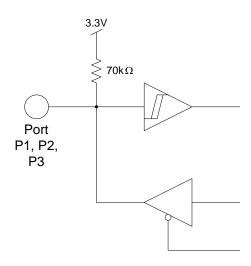

| Figure 7. Port Structure of IRMCx100 Series                                         | 29  |

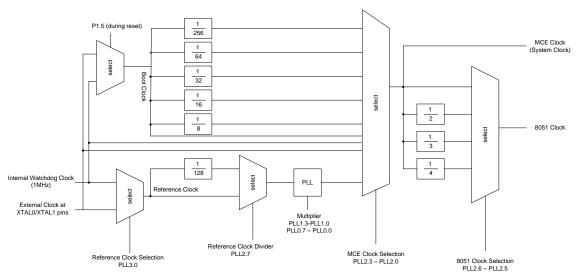

| Figure 8. Clock Selection Diagram                                                   | 34  |

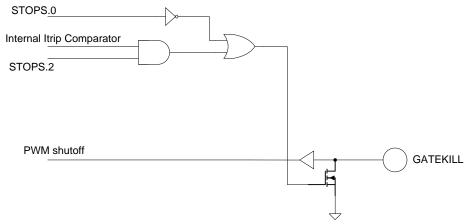

| Figure 9. GATEKILL Internal Logic                                                   | 42  |

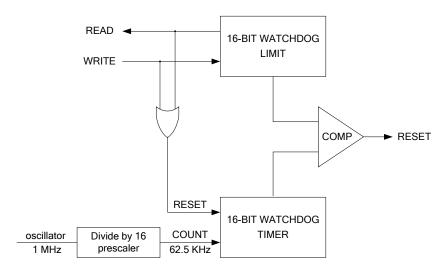

| Figure 10. Watchdog Timer                                                           |     |

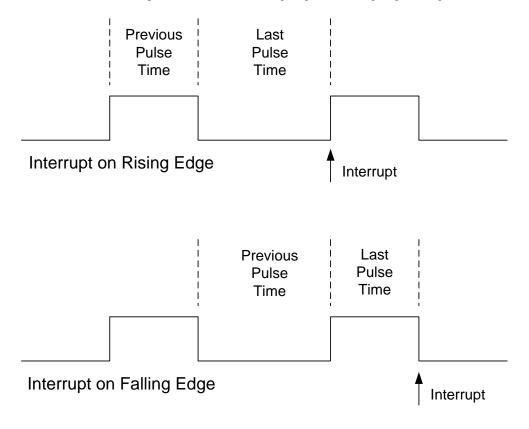

| Figure 11. Capture Timer Operation                                                  | 53  |

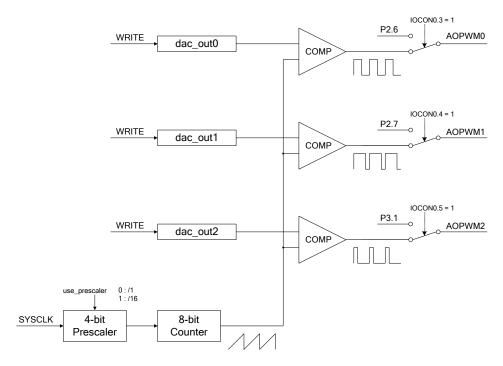

| Figure 12. D/A PWM Output                                                           |     |

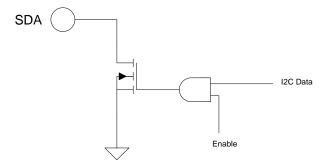

| Figure 13. I <sup>2</sup> C Pin Structure                                           |     |

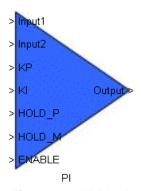

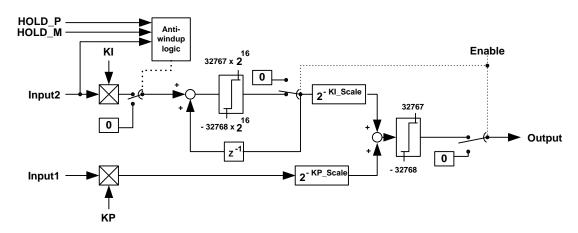

| Figure 14. PI Block                                                                 | 71  |

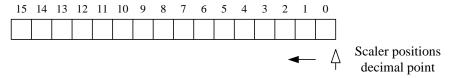

| Figure 15. LOWPASS_FILT Block                                                       | 74  |

| Figure 16. LOWPASS_FILT Frequency Response                                          |     |

| Figure 17. HIGHPASS_FILT Block                                                      |     |

| Figure 18. HIGHPASS_FILT frequency response                                         |     |

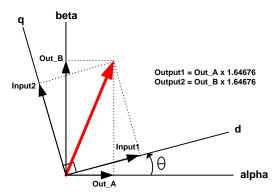

| Figure 19. VECROT Block                                                             |     |

| Figure 20. VECROT Vector Interpretation                                             |     |

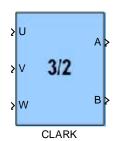

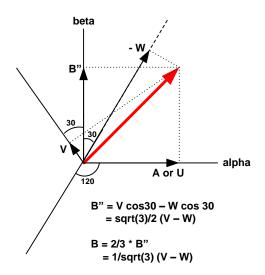

| Figure 21. CLARK Block                                                              |     |

| Figure 22. CLARK Vector Interpretation                                              |     |

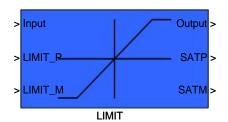

| Figure 23. LIMIT Block                                                              |     |

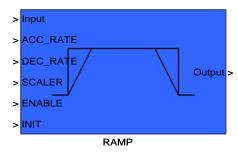

| Figure 24. RAMP Block                                                               |     |

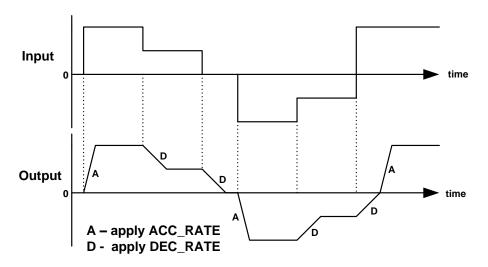

| Figure 25. ATAN Block                                                               |     |

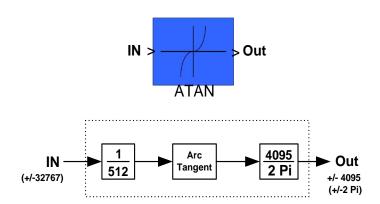

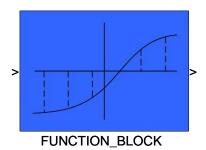

| Figure 26. FUNCTION_BLOCK Block                                                     |     |

| Figure 27. FUNCTION_BLOCK Example                                                   |     |

| Figure 28. COMPARATOR Block                                                         |     |

| Figure 29. SWITCH Block                                                             |     |

| Figure 30. BIT_LATCH Block                                                          |     |

| Figure 31. PEAK_DETECT Block                                                        |     |

| Figure 32. TRANSITION Block                                                         |     |

| Figure 33. INTEGRAL2 Block                                                          |     |

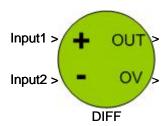

| Figure 34. DIFF Block                                                               | 93  |

| Figure 35. SUM Block                                                                |     |

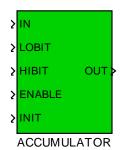

| Figure 36. ACCUMULATOR Block                                                        |     |

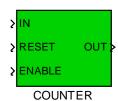

| Figure 37. COUNTER Block                                                            |     |

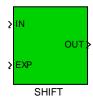

| Figure 38. SHIFT Block                                                              |     |

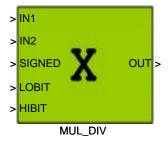

| Figure 39. MUL_DIV Block                                                            |     |

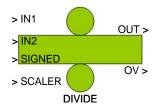

| Figure 40. DIVIDE Block                                                             |     |

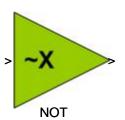

| Figure 41. NOT Block                                                                |     |

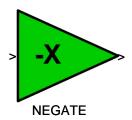

| Figure 42. NEGATE Block                                                             |     |

| Figure 43. AND Block                                                                |     |

|                                                                                     |     |

| Figure 44. OR Block                                                                 |     |

| Figure 45. XOR Block                                                                |     |

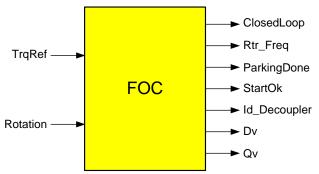

| Figure 46. SENSORLESS_FOC Block                                                     |     |

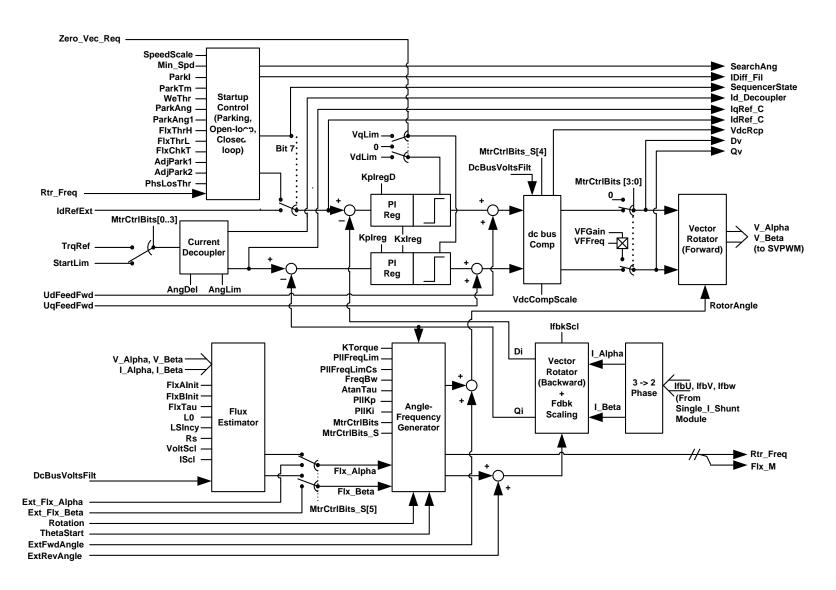

| Figure 47. SENSORLESS_FOC Block Diagram                                             |     |

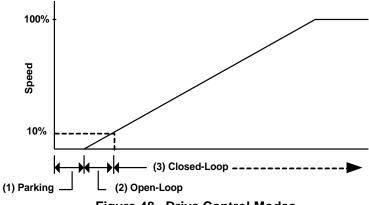

| Figure 48. Drive Control Modes                                                      |     |

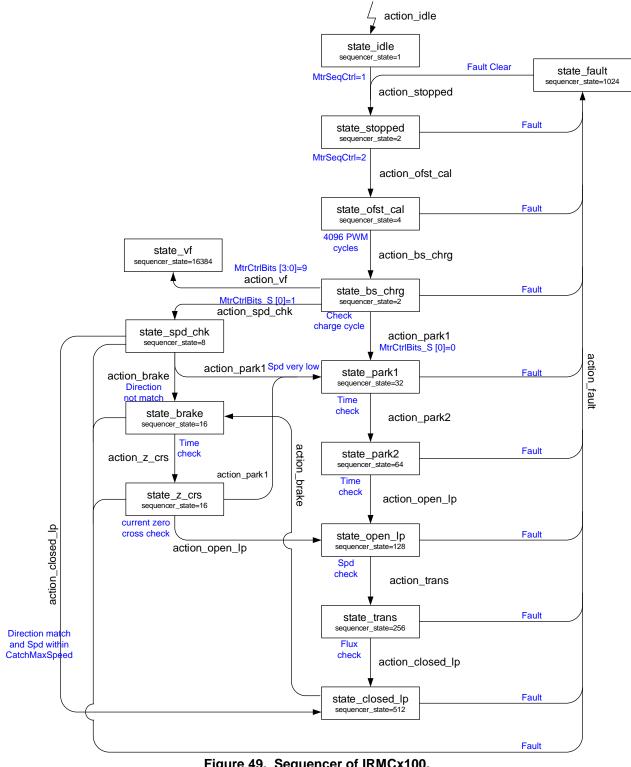

| Figure 49. Sequencer of IRMCx100.                                                   |     |

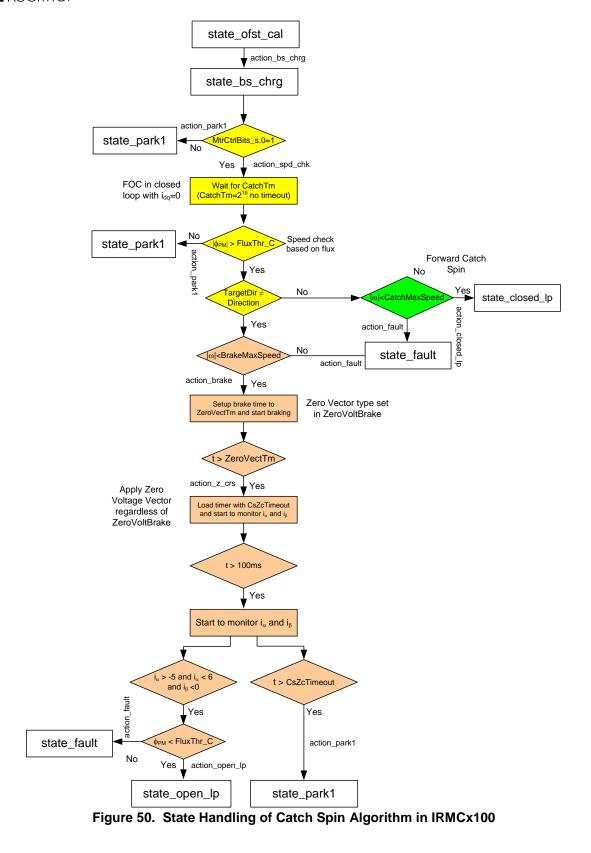

| Figure 50. State Handling of Catch Spin Algorithm in IRMCx100                       |     |

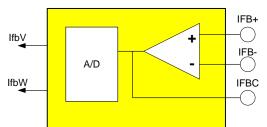

| Figure 51. CURRENT_MEAS Block                                                       |     |

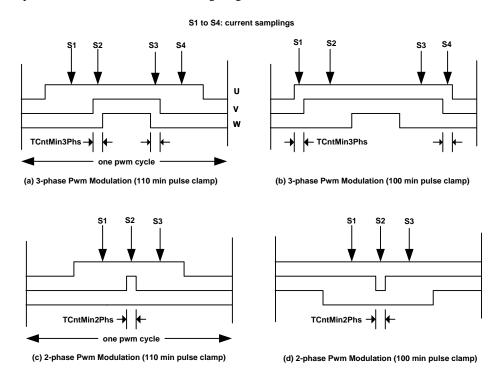

| Figure 52. Single Current Shunt Registers (TCntMin2Phs, TCntMin3Phs)                |     |

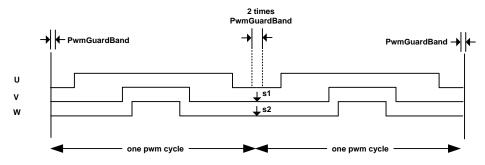

| Figure 53. Leg Shunt Register (PwmGuardBand).                                       | 114 |

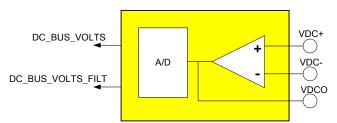

| Figure 54. | DC_BUS_VOLTAGE Block                                  | . 115 |

|------------|-------------------------------------------------------|-------|

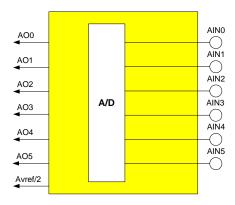

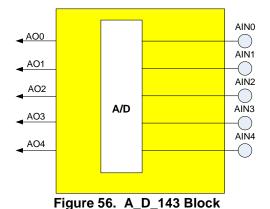

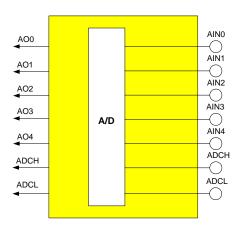

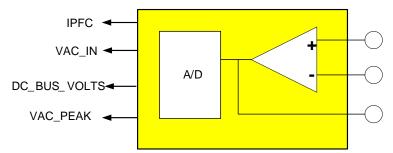

|            | A_D_171 Block                                         |       |

| Figure 56. | A_D_143 Block                                         | . 116 |

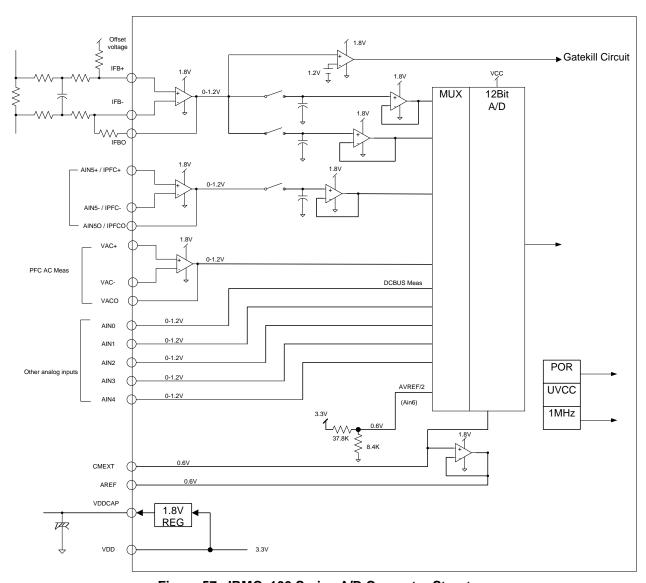

| Figure 57. | IRMCx100 Series A/D Converter Structure               | . 118 |

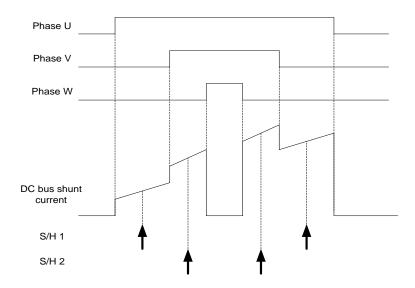

| Figure 58. | Single Shunt Current Sense Timing                     | . 119 |

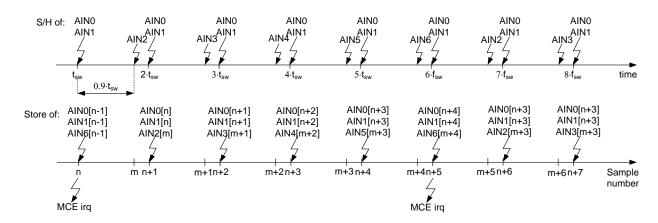

| Figure 59. | Scheduling of General Purpose A/D Channel             | . 120 |

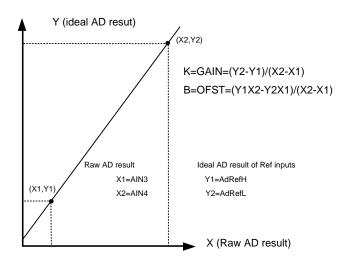

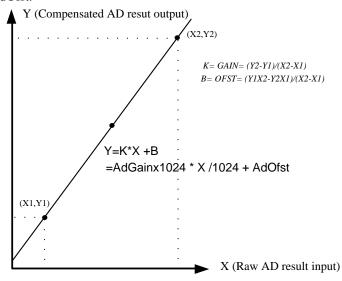

| Figure 60. | Calculation of A/D correction parameters              | . 121 |

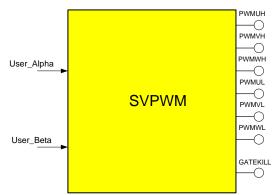

| Figure 61. | Low Loss SVPWM Block                                  | . 122 |

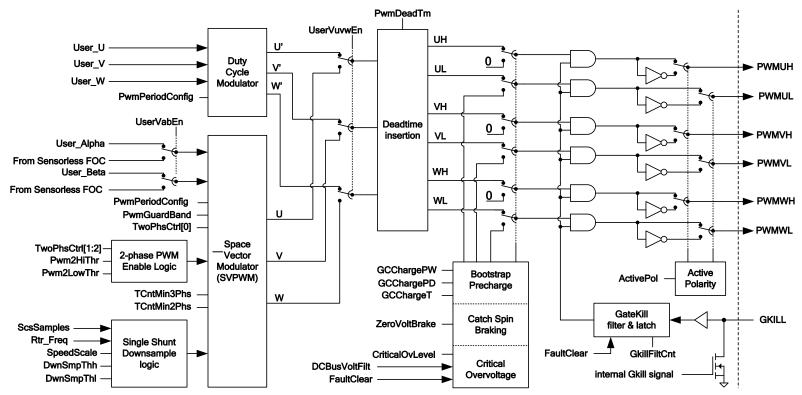

| Figure 62. | SVPWM Internal Block Diagram                          | . 124 |

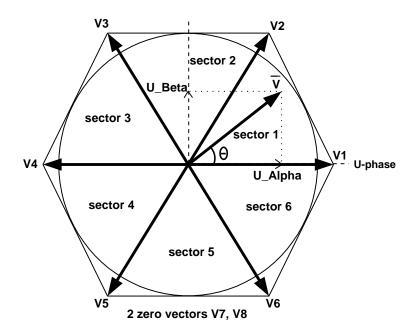

| Figure 63. | Space Vector Diagram                                  | . 125 |

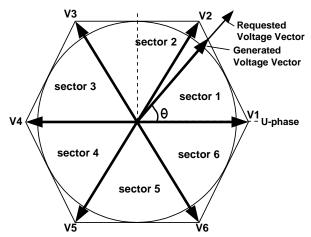

| Figure 64. | Voltage Vector Rescaling                              | . 126 |

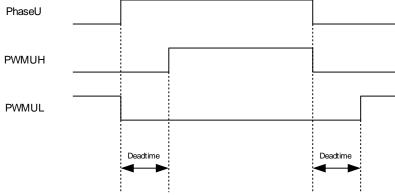

|            | Deadtime Insertion                                    |       |

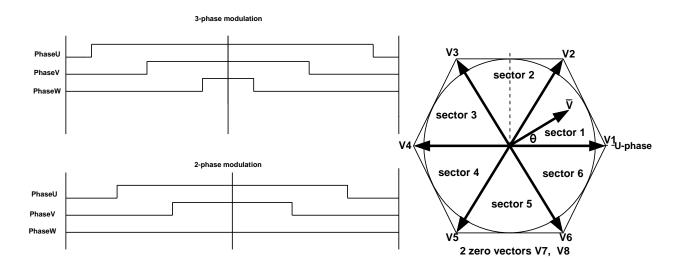

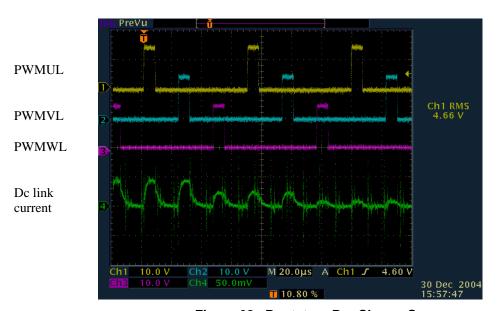

| Figure 66. | Three-Phase and Two-Phase Modulation                  | . 127 |

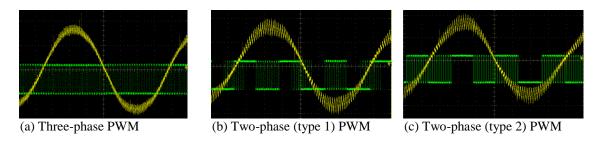

| Figure 67. | Types of Space Vector PWM                             | . 127 |

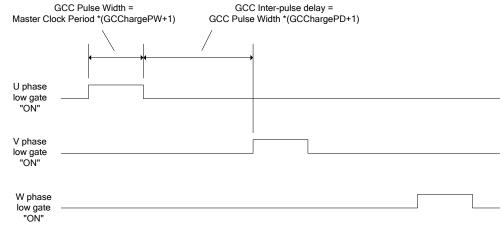

| Figure 68. | Bootstrap Pre-Charge Sequence                         | . 128 |

| Figure 69. | Timing of Bootstrap Capacitor Charging                | . 128 |

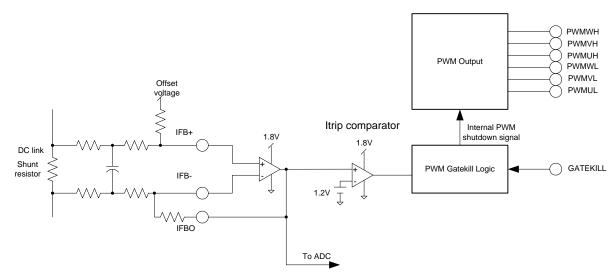

| Figure 70. | Internal Gatekill Generation                          | . 129 |

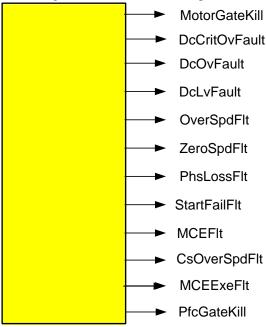

| Figure 71. | FAULTS Block                                          | . 130 |

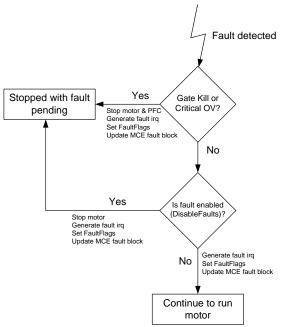

| Figure 72. | State Control of Fault Handling                       | . 132 |

|            | MCE_FAULT Block                                       |       |

|            | PFC_PWM Block                                         |       |

|            | PFC_PWM Internal Block Diagram                        |       |

|            | Generation of PFC PWM Output and ADC Timing           |       |

| Figure 77. | PFC_SENSE Block                                       | . 137 |

| Figure 78. | PFC_ AC_STATUS Block                                  | . 138 |

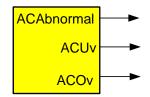

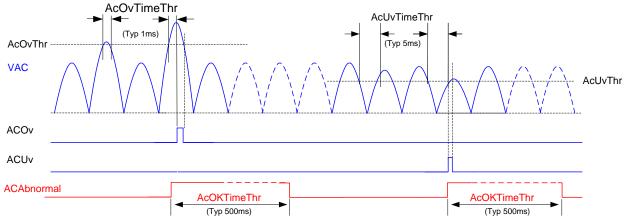

| Figure 79. | AC Over/Under Voltage Detection                       | . 138 |

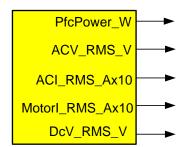

| Figure 80. | PFC_MOTOR_MISC                                        | . 139 |

|            | Calculation of VdcRcp                                 |       |

|            | Detail Scaling of PLL                                 |       |

|            | Measurement of AIN6 (AVREF/2)                         |       |

|            | Implementation of AD Compensation                     |       |

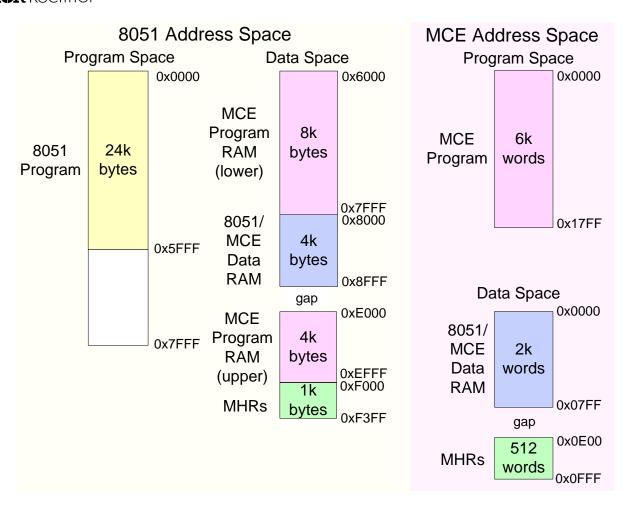

| Figure 85. | Memory Map of IRMCK100 Series                         | . 198 |

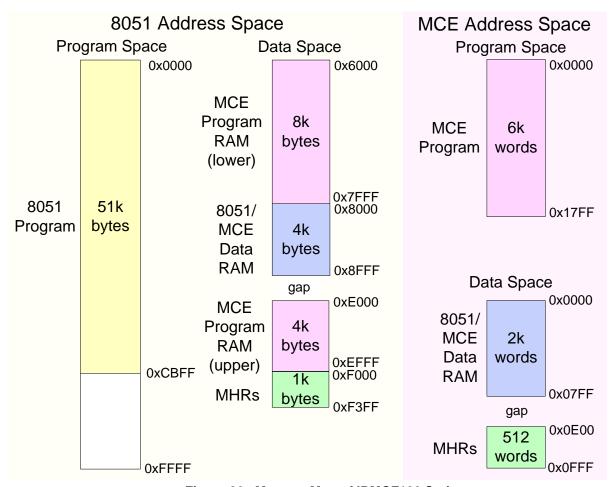

| Figure 86. | Memory Map of IRMCF100 Series                         | . 199 |

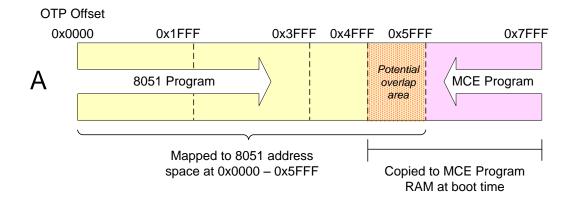

| Figure 87. | OTP Memory Usage for IRMCK100 Series                  | . 200 |

|            | Flash Memory Usage for IRMCF100 Series                |       |

|            | Timing of Sync and MCE Computation                    |       |

|            | MCE Simulink Library                                  |       |

| Figure 91. | MCE Compiler Input Screen                             | . 212 |

| Figure 92. | Example Firmware Selection Window                     | . 213 |

|            | MCE Compiler Results Example                          |       |

|            | The Host Register Summary Ûtility                     |       |

|            | The CustomMotPer Utility                              |       |

| Figure 96. | Example Model Info Block Showing Two Firmware Options | . 217 |

| Figure 97. | MCE Design Hierarchy                                  | . 219 |

## LIST OF TABLES

| Table 1. I | RMCx100 Products                       | 12 |

|------------|----------------------------------------|----|

| Table 1. A | Access to Memory Resources             | 13 |

|            | 3051 Instructions                      |    |

| Table 3. S | Special Function Register Memory Map   | 22 |

|            | Special Function Registers             |    |

|            | Peripheral Registers                   |    |

| Table 6. I | Discrete I/Os from Ports 1, 2, 3 and 5 | 28 |

| Table 7. I | nterrupt Source Summary                | 43 |

| Table 8. I | nterrupt Service Order                 | 47 |

|            | Registers for I <sup>2</sup> C         |    |

| Table 10.  | Registers for SPI                      | 62 |

|            | MCE Library Elements                   |    |

| Table 12.  | PI User Inputs and Outputs             | 73 |

|            | PI System Inputs and Outputs           |    |

| Table 14.  | PI Execution Time                      | 73 |

|            | LOWPASS_FILT User Inputs and Outputs   |    |

| Table 16.  | LOWPASS_FILT Execution Time            | 75 |

|            | HIGHPASS_FILT User Inputs and Outputs  |    |

|            | HIGHPASS_FILT Execution Time           |    |

|            | VECROT Inputs and Outputs              |    |

| Table 20.  | VECROT Execution Time                  | 79 |

| Table 21.  | CLARK Inputs and Outputs               | 80 |

|            | CLARK Execution Time                   |    |

|            | LIMIT Inputs and Outputs               |    |

|            | LIMIT Execution Time                   |    |

|            | RAMP User Inputs and Outputs           |    |

|            | RAMP Execution Time                    |    |

| Table 27.  | ATAN Inputs and Outputs                | 84 |

| Table 28.  | ATAN Execution Time                    | 84 |

| Table 29.  | FUNCTION_BLOCK Inputs and Outputs      | 86 |

| Table 30.  | FUNCTION_BLOCK Execution Time          | 86 |

| Table 31.  | COMPARATOR Inputs and Outputs          | 87 |

| Table 32.  | COMPARATOR Execution Time              | 87 |

|            | SWITCH Inputs and Outputs              |    |

|            | SWITCH Execution Time                  |    |

|            | BIT_LATCH User Inputs and Outputs      |    |

|            | BIT_LATCH Execution Time               |    |

|            | PEAK_DETECT User Inputs and Outputs    |    |

|            | PEAK_DETECT Execution Time             |    |

| Table 39.  | TRANSITION User Inputs and Outputs     | 91 |

| Table 40.  | TRANSITION Execution Time              | 91 |

|            | INTEGRAL2 User Inputs and Outputs      |    |

| Table 42.  | INTEGRAL2 Execution Time               | 92 |

|            | DIFF Inputs and Outputs                |    |

| Table 44.  | DIFF Execution Time                    | 93 |

|            | SUM Inputs and Outputs                 |    |

|            | SUM Execution Time                     |    |

|            | ACCUMULATOR User Inputs and Outputs    |    |

|            | ACCUMULATOR Execution Time             |    |

|            | COUNTER User Inputs and Outputs        |    |

| Table 50.  | COUNTER Execution Time                 | 96 |

|            | SHIFT Inputs and Outputs               |    |

| Table 52.  | SHIFT Execution Time                   | 97 |

| Table 53. | MUL_DIV Inputs and Outputs                                   | 98  |

|-----------|--------------------------------------------------------------|-----|

|           | MUL_DIV Execution Time                                       |     |

| Table 55. | DIVIDE Inputs and Outputs                                    | 100 |

|           | DIVIDE Execution Time                                        |     |

| Table 57. | NOT Inputs and Outputs                                       | 100 |

|           | NOT Execution Time                                           |     |

| Table 59. | NEGATE Inputs and Outputs                                    | 101 |

| Table 60. | NEGATE Execution Time                                        | 101 |

| Table 61. | AND Inputs and Outputs                                       | 101 |

|           | AND Execution Time                                           |     |

| Table 63. | OR Inputs and Outputs                                        | 102 |

| Table 64. | OR Execution Time                                            | 102 |

| Table 65. | XOR Inputs and Outputs                                       | 102 |

| Table 66. | XOR Execution Time                                           | 102 |

| Table 67. | SENSORLESS_FOC Available Inputs and Outputs                  | 105 |

| Table 68. | CURRENT_MEAS available Inputs and Outputs                    | 113 |

| Table 69. | DC_BUS_VOLTAGE Outputs                                       | 115 |

| Table 70. | A_D_100 Outputs                                              | 117 |

| Table 71. | LOWLOSS_SVPWM Available Inputs and Outputs                   | 123 |

| Table 72. | FAULTS Block Outputs for IRMCx100 Series                     | 130 |

|           | Summary of Fault Handling                                    |     |

| Table 74. | Relationship between System State and Active Fault Functions | 132 |

| Table 75. | MCE_FAULT Block Inputs                                       | 133 |

| Table 76. | PFC_PWM Inputs and Outputs                                   | 134 |

|           | PFC_SENSE Outputs                                            |     |

|           | . PFC_AC_STATUS Outputs                                      |     |

| Table 79. | PFC_MOTOR_MISC Outputs                                       | 139 |

| Table 80. | MCE Processor Registers                                      | 205 |

### 1. Overview

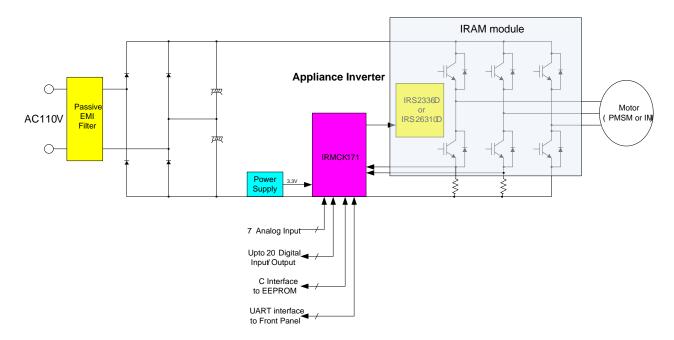

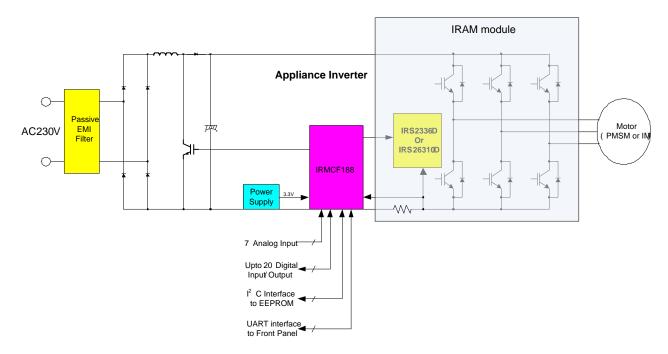

IRMCK143,IRMCF184,IRMCF188,IRMCF183,IRMCK182,IRMCK172, IRMCK171 and IRMCF171 are components of a new family of International Rectifier integrated circuit devices, collectively called the IRMCx100 series. These devices are primarily designed as one-chip solutions for complete inverterized appliance motor control applications. Unlike a traditional microcontroller or DSP, the IRMCx100-series devices provide a built-in closed loop sensorless control algorithm using the unique Motion Control Engine (MCE<sup>TM</sup>) for permanent magnet motors. The MCE<sup>TM</sup> consists of a collection of control elements, motion peripherals, a dedicated motion control sequencer and dual port RAM to map internal signal nodes. These devices also employ a unique single shunt current reconstruction circuit, in addition to two leg shunt resistor current sensing, to eliminate additional analog/digital circuitry and enable a direct shunt resistor interface to the IC. The motor can be either a permanent magnet motor or an induction motor depending on application needs, with a common control structure: Sensorless Field Oriented Control, Figure 1 shows a typical application schematic of sensorless control with two shunt current sense resistor while Figure 2 shows sensorless control with a single shunt resistor current sense configuration with power factor correction (PFC). Motion control programming is achieved using a dedicated graphical compiler integrated into the MATLAB/Simulink<sup>TM</sup> development environment. Sequencing, user interface, host communication, and upper layer control tasks can be implemented in the 8051 high-speed 8-bit microcontroller. The 8051 microcontroller is equipped with a JTAG port to facilitate emulation and debugging tools.

The IRMCK100-series devices contain 32K bytes of One Time Programmable (OTP) memory and 16K bytes RAM for instruction storage, dual port RAM for MCE-8051 communication, and local 8051 RAM. The IRMCF100-series devices replace the 32K-byte OTP memory with a 64K-byte flash memory.

Figure 1. Typical Two Shunt Leg Current Sensing Application Diagram Using IRMCx100

Figure 2. Typical Application of IRMCx188 with Single Shunt Current Sensing and PFC

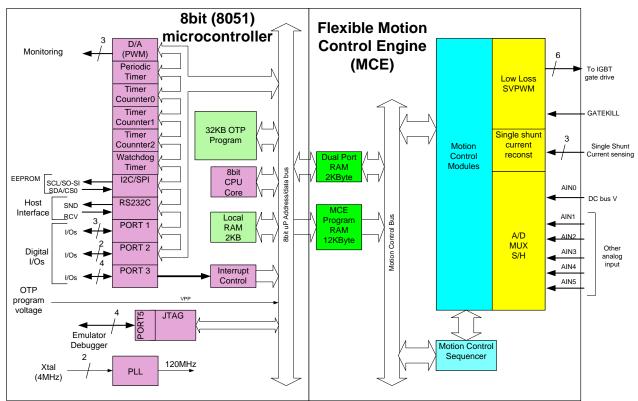

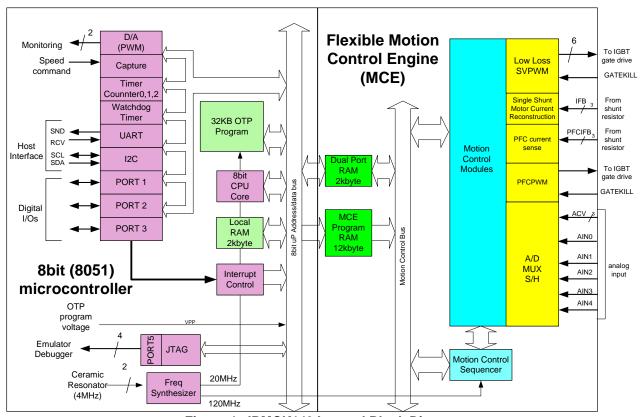

A block diagram of the IRMCK171 is shown in Figure 3. The IRMCF171 is functionally equivalent, with the 32K-byte OTP memory replaced by a 64K-byte flash memory.

Figure 3. IRMCK171 Internal Block Diagram

A block diagram of the IRMCK143 is shown in Figure 4. The IRMCF143 is functionally equivalent, with the 32K-byte OTP memory replaced by a 64K-byte flash memory.

Figure 4. IRMCK143 Internal Block Diagram

Various products offering in 100 series is listed in the table below:

| Part Number | Feature                                | Package |

|-------------|----------------------------------------|---------|

| IRMCK171    | OTP, Motor Sensorless Control          | QFP48   |

| IRMCK172    | OTP, Motor Sensorless Control          | QFN48   |

| IRMCK182    | OTP, Motor Sensorless Control          | QFN32   |

| IRMCK143    | OTP, Servo Control                     | QFP64   |

| IRMCF183    | Flash, Motor Sensorless Control        | QFN32   |

| IRMCF171    | Flash, Motor Sensorless Control        | QFP48   |

| IRMCF143    | Flash, Servo Control                   | QFP64   |

| IRMCF188    | Flash , Motor Sensorless + PFC Control | QFP64   |

Table 1. IRMCx100 Products

## 1.1 System Components

The IRMCx100-series devices can be divided into four main components, shown color-coded in Figure 3 and Figure 4. The components are:

- The 8051 microcontroller, shown at the far left in purple

- RAM and non-volatile memory for program and data storage, shown at the center of the diagram in green

- The Motion Control Engine (MCE), shown at right in blue

- Hardware interface or "motion peripheral" modules, shown at the far right in yellow

#### 1.2 Memory Resources

The IRMCx100 series provides four memory-mapped resources:

- Non-volatile memory for program storage

- RAM for MCE program execution

- RAM for 8051 and MCE data storage

- Memory-mapped motion hardware registers (MHRs)

Access to some of these resources by the MCE and 8051 is limited, as described in Table 2.

| Memory Resource           | Size (bytes) | Access by 8051 | Access by MCE  |

|---------------------------|--------------|----------------|----------------|

| OTP Memory (IRMCK1xx)     | 32K          | Read only      | None           |

| Flash Memory (IRMCF1xx)   | 64K          | Read only      | None           |

| MCE Program RAM           | 12K          | Write only     | Read only      |

| Data RAM                  | 4K           | Read and write | Read and write |

| Motion Hardware Registers | 1K           | Read and write | Read and write |

**Table 2. Access to Memory Resources**

#### 1.2.1 OTP Memory (IRMCK1xx)

For the IRMCK1xx, the 32K-byte OTP memory holds both 8051 and MCE program. The 8051 program executes directly from this area of OTP memory. The MCE cannot address OTP memory. The IRMCK100-series hardware copies MCE program from OTP to MCE program RAM during the boot process and MCE program executes from RAM. Refer to Section 1.4 for more information about the boot process.

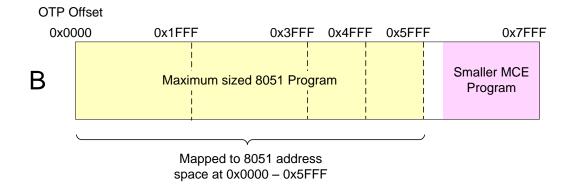

OTP memory is divided into two areas with the 8051 program contained in the first section and the MCE program contained in the second. The boundary between the two areas is dynamic and can vary from 20K bytes to 24K bytes. This allows a maximum size of 24K bytes for the 8051 program (limiting MCE program size to 8K bytes) or a maximum size of 12K bytes for the MCE program (limiting the 8051 program to 20K bytes). The total program size (8051 + MCE) cannot exceed 32K bytes. Refer to Section 4.2 for more information about the OTP memory.

#### 1.2.2 Flash Memory (IRMCF1xx)

For the IRMCF1xx, the 64K-byte flash memory holds both 8051 and MCE program. The 8051 program executes directly from this area of flash memory. The MCE cannot address flash memory. The IRMCF100-series hardware copies MCE program from flash to MCE program RAM during the boot process and MCE program executes from RAM. Refer to Section 1.4 for more information about the boot process.

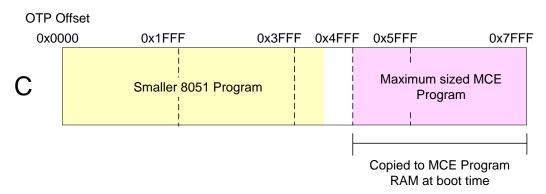

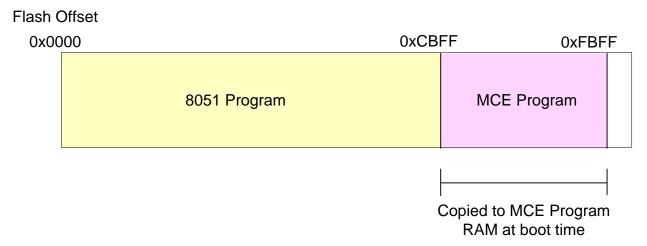

Flash memory is divided into two areas with the 8051 program contained in the first section and the MCE program contained in the second. The boundary between the two areas is fixed at offset 0xCBFF and the upper 1K bytes (beginning at offset 0xFC00) are reserved. This allows a maximum size of 51K bytes for the 8051 program and a maximum size of 12K bytes for the MCE program. Refer to Section 4.3 for more information about the flash memory.

#### 1.2.3 Data RAM

Shared data RAM for the 8051 and MCE has a total size of 4K bytes. This area is used for MCE private data storage, 8051 private data storage and shared data, such as the motion firmware registers (MFRs) described in Section 3.4. For more information about data RAM usage, refer to Section 4.4.

See Section 4.1 for information on how the memory resources described here are mapped to 8051 and MCE memory.

### 1.3 Byte Ordering

Byte ordering refers to the convention used to store 16-bit and 32-bit values in memory using a processor, such as the 8051, that has a native addressing mode of 8 bits. The two standard byte ordering conventions are "big endian" or "Motorola" byte ordering and "little endian" or "Intel" byte ordering.

In big endian byte ordering, the "big end" of a value is stored first. That is, the high order byte is stored at the lowest memory address and the low-order byte is stored at the highest memory address. In little endian byte ordering, the "little end" is stored first, with the low-order byte at the lowest memory address.

For example, suppose the 16-bit value 0x2345 is to be stored in memory at address 0x1000. Using big endian byte ordering, 0x23 is stored at address 0x1000 and 0x45 is stored at address 0x1001. Using little endian byte ordering, 0x45 is stored at address 0x1000 and 0x23 is stored at address 0x1001.

The table below shows how the value 0x456789AB would be stored at address 0x1000 using each of the byte ordering conventions.

| Address | Big Endian | Little Endian |

|---------|------------|---------------|

| 1000    | 45         | AB            |

| 1001    | 67         | 89            |

| 1002    | 89         | 67            |

| 1003    | AB         | 45            |

The Keil compiler used for 8051 software development generates code that uses big endian byte ordering to store 16-bit and 32-bit values in memory.

The MCE is a 16-bit processor and uses little endian byte ordering for data storage. The smallest unit of data storage on the MCE processor is 16 bits (it cannot access a single byte in memory). The shared RAM used to exchange information between the 8051 and MCE processors is 8-bit addressable to the 8051, but 16-bit addressable to the MCE.

All data shared between the 8051 and MCE processors is expected to be in little endian byte ordering. This means that the 8051 must swap bytes before writing to shared RAM and swap bytes after reading from shared RAM. The table below shows how the value 0x456789AB would be stored at address 0x8200 in 8051 RAM, which corresponds to address 0x0100 in MCE RAM. Note that the 8051 reads and writes a byte at a time, but the MCE always accesses the memory a word (16 bits) at a time.

| 8051 Address | 8051 Bytes | MCE Address | MCE Words |

|--------------|------------|-------------|-----------|

| 8200         | AB         | 0100        | 89AB      |

| 8201         | 89         |             |           |

| 8202         | 67         | 0101        | 4567      |

| 8203         | 45         |             |           |

#### 1.4 Reset Mechanism and Boot Process

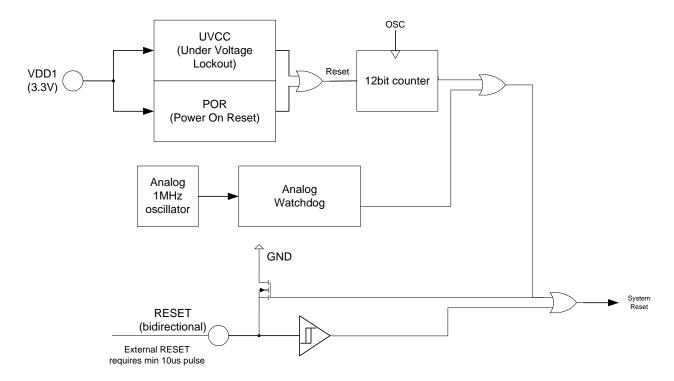

A power on reset does not require any assertion of reset signal from an external circuit. The IRMCx100 series contains an analog power on reset (POR) circuit which issues reset to all internal circuits. Therefore no filter is required at the reset pin. The reset pin is bidirectional and becomes output when one of the following conditions occurs.

- 1) The watchdog timer times out.

- 2) Under voltage lockout (UVCC) detects low voltage on 3.3V.

- 3) Power up

Among these, cases (2) and (3) generate RESET low assertion for a period of 2048 crystal clock time. When the watchdog timeout occurs, RESET low assertion time becomes 31 usec.

When the RESET input is asserted from an external source, minimum 10 usec low level assertion pulse is required to ensure the internal reset.

Figure 5 shows the Reset Module, which contains two analog circuits, namely Under Voltage Lockout (UVCC) and Power On Reset (POR), and a 12-bit ripple counter to stretch the Reset pulse width. This module is also shown in Figure 6.

Figure 5. Reset Module

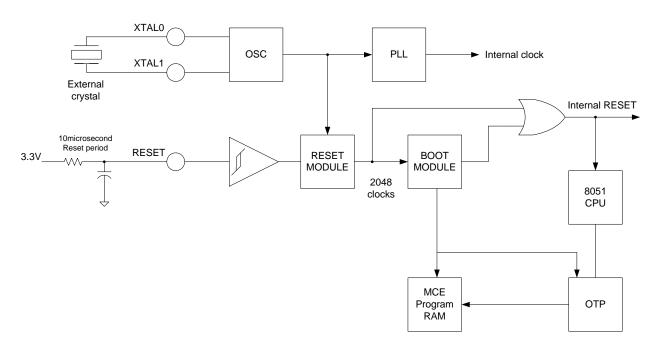

The reset and boot processes are closely tied together. The boot process is automatically accomplished following a proper reset sequence, which is triggered by power on or external RESET. Therefore, a user application cannot intervene during the reset and boot process. The main task of the boot process is to copy the MCE program stored in internal OTP or flash memory to MCE program RAM, initialize the program counter and transfer control to the 8051 CPU. The block diagram of the reset and boot process is shown in Figure 6.

A reset of the device is accomplished by asserting low on the RESET input pin for a minimum of 10 µsec. The RESET is a Schmitt trigger type input with hysteresis to avoid any multiple triggers to the system. Once the reset is recognized in the system, the reset module counts up 2048 clocks at the crystal frequency to ensure that the internal PLL becomes stable for generation of the internal system clock. When this waiting period is complete, the boot sequence is initiated.

Figure 6. Reset and Boot Process

#### For the IRMCK1xx, the boot sequence is done in the following way:

- The boot clock source is determined according to the value of VPP/P1.5 when the reset module signal is deasserted:

- o VPP/P1.5 = 0 : boot\_clock = 1MHz oscillator (watchdog) clock

- o VPP/P1.5 = 1 : boot clock = crystal clock

- The boot sequence starts 16 boot\_clocks after reset module signal is de-asserted.

- OTP bytes from offsets 0x7FFE and 0x7FFD are decrypted and written to the 16-bit word at address 0x000 of the MCE program RAM.

- OTP bytes from offsets 0x7FFC and 0x7FFB are decrypted and written to the 16-bit word at address 0x001 of the MCE program RAM.

- This copy procedure continues until the last MCE program bytes are copied from OTP offsets 0x5000 and 0x4FFF to MCE program RAM address 0x17FF.

- A total of 12K bytes are copied.

- Only after the boot sequence is done does the 8051 code start running.

#### For the IRMCF1xx, the boot sequence is similar, but the address range for the MCE program is different:

- The boot clock source is determined according to the value of P1.5 when the reset module signal is de-asserted:

- o P1.5 = 0 : boot\_clock = 1MHz oscillator (watchdog) clock

- o P1.5 = 1 : boot\_clock = crystal clock

- The boot sequence starts 16 boot\_clocks after reset module signal is de-asserted.

- Flash bytes from offsets 0xFBFE and 0xFBFD are decrypted and written to the 16-bit word at address 0x000 of the MCE program RAM.

- Flash bytes from offsets 0xFBFC and 0xFBFB are decrypted and written to the 16-bit word at address 0x001 of the MCE program RAM.

- This copy procedure continues until the last MCE program bytes are copied from flash offsets 0xCC00 and 0xCBFF to MCE program RAM address 0x17FF.

- A total of 12K bytes are copied.

- Only after the boot sequence is done does the 8051 code start running.

Refer to Section 4.2 for a more detailed description of the copy procedure.

## IRMCx100 Reference Manual

#### **Boot time:**

Total MCE program to be copied: 12 \* 1024 bytes

Number of clk periods to transfer one byte (including synchronizers and decryption logic): 20

Boot clock freq: 1MHz for internal watchdog clock / 4MHz as example of an external crystal oscillator.

Total transfer time (1MHZ) =  $12 * 1024 * 20 * 1 \mu sec = 244 msec$ Total transfer time (4MHZ) =  $12 * 1024 * 20 * 0.25 \mu sec = 61 msec$

The boot module holds the internal RESET active while data transfer takes place, then it releases the internal RESET upon completion of the copy process. Immediately after the copy process completes, the 8051 application program begins execution.

## 2 8051 Microcontroller

This section describes IRMCx100-series features and functions that are specific to the 8051 microcontroller. The interface between the 8051 and the MCE is covered in Section 4.

The instruction set and basic operation of the IRMCx100 series 8051 microcontroller is consistent with the standard Intel 8051 processor. A number of peripheral devices and special functions have been added to customize the operation for the intended application.

#### 2.1 Instruction Set

The instructions of the 8051 microcontroller are 1, 2 or 3 bytes long as listed in the 'Bytes' column below. Each instruction takes either one, two or four PCLK cycles to execute as listed in the following table (one PCLK cycle is equal to two 8051 clock cycles).

Table 3 lists the 8051 instructions. In the table, an entry such as E8-EF indicates a continuous block of hex opcodes used for 8 different registers, the register numbers of which are defined by the lowest three bits of the corresponding code. Non-continuous blocks of codes, shown as  $11 \rightarrow F1$  (for example), are used for absolute jumps and calls, with the top 3 bits of the code being used to store the top three bits of the destination address.

The CJNE instructions use the abbreviation #d for immediate data; other instructions use #data.

| ARITHMETIC   |                                             |       |                |          |  |  |  |

|--------------|---------------------------------------------|-------|----------------|----------|--|--|--|

| Mnemonic     | Description                                 | Bytes | PCLK<br>Cycles | Hex code |  |  |  |

| ADD A,Rn     | Add register to A                           | 1     | 1              | 28-2F    |  |  |  |

| ADD A,dir    | Add direct byte to A                        | 2     | 1              | 25       |  |  |  |

| ADD A,@Ri    | Add indirect memory to A                    | 1     | 1              | 26-27    |  |  |  |

| ADD A,#data  | Add immediate to A                          | 2     | 1              | 24       |  |  |  |

| ADDC A,Rn    | Add register to A with carry                | 1     | 1              | 38-3F    |  |  |  |

| ADDC A,dir   | Add direct byte to A with carry             | 2     | 1              | 35       |  |  |  |

| ADDC A,@Ri   | Add indirect memory to A with carry         | 1     | 1              | 36-37    |  |  |  |

| ADDC A,#data | Add immediate to A with carry               | 2     | 1              | 34       |  |  |  |

| SUBB A,Rn    | Subtract register from A with borrow        | 1     | 1              | 98-9F    |  |  |  |

| SUBB A,dir   | Subtract direct byte from A with borrow     | 2     | 1              | 95       |  |  |  |

| SUBB A,@Ri   | Subtract indirect memory from A with borrow | 1     | 1              | 96-97    |  |  |  |

| SUBB A,#data | Subtract immediate from A with borrow       | 2     | 1              | 94       |  |  |  |

| INC A        | Increment A                                 | 1     | 1              | 04       |  |  |  |

| INC Rn       | Increment register                          | 1     | 1              | 08-0F    |  |  |  |

| INC dir      | Increment direct byte                       | 2     | 1              | 05       |  |  |  |

| INC @Ri      | Increment indirect memory                   | 1     | 1              | 06-07    |  |  |  |

| DEC A        | Decrement A                                 | 1     | 1              | 14       |  |  |  |

| DEC Rn       | Decrement register                          | 1     | 1              | 18-1F    |  |  |  |

| DEC dir      | Decrement direct byte                       | 2     | 1              | 15       |  |  |  |

| DEC @Ri      | Decrement indirect memory                   | 1     | 1              | 16-17    |  |  |  |

| INC DPTR     | Increment data pointer                      | 1     | 2              | A3       |  |  |  |

| MUL AB       | Multiply A by B                             | 1     | 4              | A4       |  |  |  |

| DIV AB       | Divide A by B                               | 1     | 4              | 84       |  |  |  |

| DA A         | Decimal Adjust A                            | 1     | 1              | D4       |  |  |  |

| LOGICAL       |                                       |       |                |          |  |  |  |

|---------------|---------------------------------------|-------|----------------|----------|--|--|--|

| Mnemonic      | Description                           | Bytes | PCLK<br>Cycles | Hex code |  |  |  |

| ANL A,Rn      | AND register to A                     | 1     | 1              | 58-5F    |  |  |  |

| ANL A,dir     | AND direct byte to A                  | 2     | 1              | 55       |  |  |  |

| ANL A,@Ri     | AND indirect memory to A              | 1     | 1              | 56-57    |  |  |  |

| ANL A,#data   | AND immediate to A                    | 2     | 1              | 54       |  |  |  |

| ANL dir,A     | AND A to direct byte                  | 2     | 1              | 52       |  |  |  |

| ANL dir,#data | AND immediate to direct byte          | 3     | 2              | 53       |  |  |  |

| ORL A,Rn      | OR register to A                      | 1     | 1              | 48-4F    |  |  |  |

| ORL A,dir     | OR direct byte to A                   | 2     | 1              | 45       |  |  |  |

| ORL A,@Ri     | OR indirect memory to A               | 1     | 1              | 46-47    |  |  |  |

| ORL A,#data   | OR immediate to A                     | 2     | 1              | 44       |  |  |  |

| ORL dir,A     | OR A to direct byte                   | 2     | 1              | 42       |  |  |  |

| ORL dir,#data | OR immediate to direct byte           | 3     | 2              | 43       |  |  |  |

| XRL A,Rn      | Exclusive-OR register to A            | 1     | 1              | 68-6F    |  |  |  |

| XRL A,dir     | Exclusive-OR direct byte to A         | 2     | 1              | 65       |  |  |  |

| XRL A,@Ri     | Exclusive-OR indirect memory to A     | 1     | 1              | 66-67    |  |  |  |

| XRL A,#data   | Exclusive-OR immediate to A           | 2     | 1              | 64       |  |  |  |

| XRL dir,A     | Exclusive-OR A to direct byte         | 2     | 1              | 62       |  |  |  |

| XRL dir,#data | Exclusive-OR immediate to direct byte | 3     | 2              | 63       |  |  |  |

| CLR A         | Clear A                               | 1     | 1              | E4       |  |  |  |

| CPL A         | Complement A                          | 1     | 1              | F4       |  |  |  |

| SWAP A        | Swap Nibbles of A                     | 1     | 1              | C4       |  |  |  |

| RL A          | Rotate A left                         | 1     | 1              | 23       |  |  |  |

| RLC A         | Rotate A left through carry           | 1     | 1              | 33       |  |  |  |

| RR A          | Rotate A right                        | 1     | 1              | 03       |  |  |  |

| RRC A         | Rotate A right through carry          | 1     | 1              | 13       |  |  |  |

| DATA TRANSFER  |                                     |       |                |          |  |  |  |

|----------------|-------------------------------------|-------|----------------|----------|--|--|--|

| Mnemonic       | Description                         | Bytes | PCLK<br>Cycles | Hex code |  |  |  |

| MOV A,Rn       | Move register to A                  | 1     | 1              | E8-EF    |  |  |  |

| MOV A,dir      | Move direct byte to A               | 2     | 1              | E5       |  |  |  |

| MOV A,@Ri      | Move indirect memory to A           | 1     | 1              | E6-E7    |  |  |  |

| MOV A,#data    | Move immediate to A                 | 2     | 1              | 74       |  |  |  |

| MOV Rn,A       | Move A to register                  | 1     | 1              | F8-FF    |  |  |  |

| MOV Rn,dir     | Move direct byte to register        | 2     | 2              | A8-AF    |  |  |  |

| MOV Rn,#data   | Move immediate to register          | 2     | 1              | 78-7F    |  |  |  |

| MOV dir,A      | Move A to direct byte               | 2     | 1              | F5       |  |  |  |

| MOV dir,Rn     | Move register to direct byte        | 2     | 2              | 88-8F    |  |  |  |

| MOV dir,dir    | Move direct byte to direct byte     | 3     | 2              | 85       |  |  |  |

| MOV dir,@Ri    | Move indirect memory to direct byte | 2     | 2              | 86-87    |  |  |  |

| MOV dir,#data  | Move immediate to direct byte       | 3     | 2              | 75       |  |  |  |

| MOV @Ri,A      | Move A to indirect memory           | 1     | 1              | F6-F7    |  |  |  |

| MOV @Ri,dir    | Move direct byte to indirect memory | 2     | 2              | A6-A7    |  |  |  |

| MOV @Ri,#data  | Move immediate to indirect memory   | 2     | 1              | 76-77    |  |  |  |

| MOV DPTR,#data | Move immediate to data pointer      | 3     | 2              | 90       |  |  |  |

| MOVC A,@A+DPTR | Move code byte relative DPTR to A   | 1     | 2              | 93       |  |  |  |

| MOVC A,@A+PC   | Move code byte relative PC to A     | 1     | 2              | 83       |  |  |  |

| MOVX A,@Ri     | Move external data(A8) to A         | 1     | 2              | E2-E3    |  |  |  |

| DATA TRANSFER |                                       |   |   |       |  |  |  |

|---------------|---------------------------------------|---|---|-------|--|--|--|

| MOVX A,@DPTR  | Move external data(A16) to A          | 1 | 2 | E0    |  |  |  |

| MOVX @Ri,A    | Move A to external data(A8)           | 1 | 2 | F2-F3 |  |  |  |

| MOVX @DPTR,A  | Move A to external data(A16)          | 1 | 2 | F0    |  |  |  |

| PUSH dir      | Push direct byte onto stack           | 2 | 2 | C0    |  |  |  |

| POP dir       | Pop direct byte from stack            | 2 | 2 | D0    |  |  |  |

| XCH A,Rn      | Exchange A and register               | 1 | 1 | C8-CF |  |  |  |

| XCH A,dir     | Exchange A and direct byte            | 2 | 1 | C5    |  |  |  |

| XCH A,@Ri     | Exchange A and indirect memory        | 1 | 1 | C6-C7 |  |  |  |

| XCHD A,@Ri    | Exchange A and indirect memory nibble | 1 | 1 | D6-D7 |  |  |  |

| BOOLEAN    |                                 |       |                |          |  |  |  |

|------------|---------------------------------|-------|----------------|----------|--|--|--|

| Mnemonic   | Description                     | Bytes | PCLK<br>Cycles | Hex code |  |  |  |

| CLR C      | Clear carry                     | 1     | 1              | C3       |  |  |  |

| CLR bit    | Clear direct bit                | 2     | 1              | C2       |  |  |  |

| SETB C     | Set carry                       | 1     | 1              | D3       |  |  |  |

| SETB bit   | Set direct bit                  | 2     | 1              | D2       |  |  |  |

| CPL C      | Complement carry                | 1     | 1              | В3       |  |  |  |

| CPL bit    | Complement direct bit           | 2     | 1              | B2       |  |  |  |

| ANL C,bit  | AND direct bit to carry         | 2     | 2              | 82       |  |  |  |

| ANL C,/bit | AND direct bit inverse to carry | 2     | 2              | В0       |  |  |  |

| ORL C,bit  | OR direct bit to carry          | 2     | 2              | 72       |  |  |  |

| ORL C,/bit | OR direct bit inverse to carry  | 2     | 2              | A0       |  |  |  |

| MOV C,bit  | Move direct bit to carry        | 2     | 1              | A2       |  |  |  |

| MOV bit,C  | Move carry to direct bit        | 2     | 2              | 92       |  |  |  |

| BRANCHING       |                                          |       |                |          |  |  |

|-----------------|------------------------------------------|-------|----------------|----------|--|--|

| Mnemonic        | Description                              | Bytes | PCLK<br>Cycles | Hex code |  |  |

| ACALL addr 11   | Absolute jump to subroutine              | 2     | 2              | 11→F1    |  |  |

| LCALL addr 16   | Long jump to subroutine                  | 3     | 2              | 12       |  |  |

| RET             | Return from subroutine                   | 1     | 2              | 22       |  |  |

| RETI            | Return from interrupt                    | 1     | 2              | 32       |  |  |

| AJMP addr 11    | Absolute jump unconditional              | 2     | 2              | 01→E1    |  |  |

| LJMP addr 16    | Long jump unconditional                  | 3     | 2              | 02       |  |  |

| SJMP rel        | Short jump (relative address)            | 2     | 2              | 80       |  |  |

| JC rel          | Jump on carry = 1                        | 2     | 2              | 40       |  |  |

| JNC rel         | Jump on carry = 0                        | 2     | 2              | 50       |  |  |

| JB bit,rel      | Jump on direct bit = 1                   | 3     | 2              | 20       |  |  |

| JNB bit,rel     | Jump on direct bit $= 0$                 | 3     | 2              | 30       |  |  |

| JBC bit,rel     | Jump on direct bit = 1 and clear         | 3     | 2              | 10       |  |  |

| JMP @A+DPTR     | Jump indirect relative DPTR              | 1     | 2              | 73       |  |  |

| JZ rel          | Jump on accumulator = 0                  | 2     | 2              | 60       |  |  |

| JNZ rel         | Jump on accumulator $\neq 0$             | 2     | 2              | 70       |  |  |

| CJNE A,dir,rel  | Compare A, direct jne relative           | 3     | 2              | B5       |  |  |

| CJNE A,#d,rel   | Compare A,immediate jne relative         | 3     | 2              | B4       |  |  |

| CJNE Rn,#d,rel  | Compare register, immediate jne relative | 3     | 2              | B8-BF    |  |  |

| CJNE @Ri,#d,rel | Compare indirect, immediate jne relative | 3     | 2              | B6-B7    |  |  |

| DJNZ Rn,rel     | Decrement register, jnz relative         | 2     | 2              | D8-DF    |  |  |

| DJNZ dir,rel    | Decrement direct byte, jnz relative      | 3     | 2              | D5       |  |  |

| MISCELLANEOUS |              |       |                |          |  |

|---------------|--------------|-------|----------------|----------|--|

| Mnemonic      | Description  | Bytes | PCLK<br>Cycles | Hex code |  |

| NOP           | No operation | 1     | 1              | 00       |  |

| ADDITIONAL INSTRUCTIONS ( selected through EO bit 4 ) |                                                                    |                |          |    |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------------------|----------------|----------|----|--|--|--|

| Mnemonic                                              | Bytes                                                              | PCLK<br>Cycles | Hex code |    |  |  |  |

| MOVC @(DPTR++),A                                      | Supports software download into program memory (see Section 2.4.5) | 1              | 2        | A5 |  |  |  |

| TRAP                                                  | Software break command (see Section 2.4.5)                         | 1              | 1        | A5 |  |  |  |

Table 3. 8051 Instructions

### 2.2 Special Function Registers

I/O functions, interrupt control and some peripherals are accessed via Special Function Registers (SFRs). These registers occupy direct Internal Data Memory space locations in the range 0x80 to 0xFF. Internal processor registers (accumulator, stack pointer, etc.) can also be accessed through SFRs.

Note 1. WKTMR in the IRMCK1xx is replaced by FLSEL in the IRMCF1xx.

Table 4 shows a summary of the SFR memory map and identifies the bit-addressable registers. Table 5 lists each register individually, shows its value on reset and references the document section that describes the register in detail. Some registers are present only for certain product types, as indicated in the Notes column of Table 5 and in the detailed register descriptions.

In the detailed register descriptions, special function registers are shown shaded with a green color.

| 111 1110 1 | actanea regiot | er description | is, special ran | etion register | s are snown s | naaca wiin a giv | con color.  |                       |

|------------|----------------|----------------|-----------------|----------------|---------------|------------------|-------------|-----------------------|

|            | 0(8)           | 1(9)           | 2(A)            | 3(B)           | <b>4(C)</b>   | <b>5(D)</b>      | <b>6(E)</b> | <b>7</b> ( <b>F</b> ) |

| 80         | P0             | SP             | DPL             | DPH            |               |                  |             |                       |

| 88         | TCON           | TMOD           | TL0             | TL1            | TH0           | TH1              |             |                       |

| 90         | P1             | P1DIR          |                 |                |               |                  |             |                       |

| 98         |                |                |                 |                |               |                  |             |                       |

| A0         | P2             | P2DIR          | EO              | FLDWR          |               |                  |             |                       |

| A8         | IE             | PSCL           | IOCON0          | IOCON1         |               |                  |             |                       |

| В0         | Р3             | P3DIR          | HWCFG           | SHTEST         |               |                  |             |                       |

| B8         | IP             |                |                 |                |               |                  |             |                       |

| C0         | IS             |                |                 |                | SLPTMR        | WKTMR/           |             |                       |

|            |                |                |                 |                |               | $FLSEL^1$        |             |                       |

| C8         | T2CON          |                | RCP2L           | RCP2H          | TL2           | TH2              |             |                       |

| D0         | PSW            |                |                 |                |               | PLLF0            | PLLF1       | PLLF2                 |

| D8         |                | MCEBL          | MCEBH           | PLLF3          | HWREV         | PLLF4            | INDCOH      | INDCOL                |

| E0         | ACC            | FLDRD          |                 | MCESL          | MCESH         | STOPS            |             | P5                    |

| E8         | IE1            | MCECD0         | MCECD1          | MCECD2         | MCECD3        |                  |             |                       |

| F0         | В              |                |                 |                |               |                  |             |                       |

| F8         | IP1            |                |                 |                |               |                  |             |                       |

|            | Bit            |                | •               | •              | •             | •                | •           | •                     |

|            | Addressable    | I              |                 |                |               |                  |             |                       |

Note 1. WKTMR in the IRMCK1xx is replaced by FLSEL in the IRMCF1xx.

**Table 4. Special Function Register Memory Map**

|         |        |                                 | Reset     | Bit      |                                  |          |

|---------|--------|---------------------------------|-----------|----------|----------------------------------|----------|

| Address | Label  | Description                     | Value     | Address- | Notes                            | Document |

| (hex)   |        |                                 | (hex)     | able     |                                  | Section  |

| 80      | P0     | Port 0                          | FF        | *        | Not used                         |          |

| 81      | SP     | Stack Pointer                   | 07        |          |                                  | 2.4.1    |

| 82      | DPL    | Data Pointer Low Byte           | 00        |          |                                  | 2.4.1    |

| 83      | DPH    | Data Pointer High Byte          | 00        |          |                                  | 2.4.1    |

| 88      | TCON   | Timer/Counter Control           | 00        | *        |                                  | 2.6.2    |

| 89      | TMOD   | Timer/Counter Mode Control      | 00        |          |                                  | 2.6.2    |

| 8A      | TL0    | Timer/Counter 0 Low Byte        | 00        |          |                                  | 2.6.2    |

| 8B      | TL1    | Timer/Counter 1 Low Byte        | 00        |          |                                  | 2.6.2    |

| 8C      | TH0    | Timer/Counter 0 High Byte       | 00        |          |                                  | 2.6.2    |

| 8D      | TH1    | Timer/Counter 1 High Byte       | 00        |          |                                  | 2.6.2    |

| 90      | P1     | Port 1                          | FF        | *        |                                  | 2.4.2    |

| 91      | P1DIR  | Port 1 Direction Register       | 00        |          |                                  | 2.4.2    |

| A0      | P2     | Port 2                          | FF        | *        |                                  | 2.4.2    |

| A1      | P2DIR  | Port 2 Direction Register       | 00        |          |                                  | 2.4.2    |

| A2      | EO     | Extended Operation Register     | 00        |          |                                  | 2.4.5    |

| A3      | FLDWR  | Flash Write Data                | 00        |          | Internal use<br>IRMCF1xx<br>only |          |

| A8      | ΙE     | Interrupt Enable Register 0     | 00        | *        | ,                                | 2.5.3    |

| A9      | PSCL   | Prescaler Control               | 00        |          |                                  | 2.6.1    |

| AA      | IOCON0 | I/O Control Register 0          | В0        |          |                                  | 2.4.2    |

| AB      | IOCON1 | I/O Control Register 1          | 00        |          |                                  | 2.4.2    |

| В0      | P3     | Port 3                          | FF        | *        |                                  | 2.4.2    |

| B1      | P3DIR  | Port 3 Direction Register       | 00        |          |                                  | 2.4.2    |

| B2      | HWCFG  | Hardware Configuration          | 01        |          |                                  | 2.4.5    |

| В3      | SHTEST | Sample & Hold Test Enable       | 00        |          |                                  |          |

| В8      | IP     | Interrupt Priority Register 0   | 00        | *        |                                  | 2.5.4    |

| C0      | IS     | Interrupt Status & Acknowledge  | 00        | *        |                                  | 2.5.3    |

| C4      | SLPTMR | Power saving mode sleep timer   | 00        |          |                                  | 2.4.4    |

| C5      | WKTMR  | Power saving mode wake up timer | 00        |          | IRMCK1xx<br>only                 | 2.4.4    |

| C5      | FLSEL  | Flash Select Register           | 00        |          | Internal use<br>IRMCF1xx<br>only |          |

| C8      | T2CON  | Timer /Counter 2 Control        | 00        | *        |                                  | 2.6.2    |

| CA      | RCP2L  | Timer 2 Capture Register Low    | 00        |          |                                  | 2.6.2    |

| СВ      | RCP2H  | Timer 2 Capture Register High   | 00        |          |                                  | 2.6.2    |

| CC      | TL2    | Timer /Counter 2 Low Byte       | 00        |          |                                  | 2.6.2    |

| CD      | TH2    | Timer /Counter 2 High Byte      | 00        |          |                                  | 2.6.2    |

| D0      | PSW    | Program Status Word             | 00        | *        |                                  | 2.4.1    |

| D5      | PLLF0  | PLL Setup                       | Device    |          |                                  | 2.4.3    |

|         |        | bits $0-7$                      | dependent |          |                                  |          |

| D6      | PLLF1  | PLL Setup                       | Device    |          |                                  | 2.4.3    |

|         |        | bits 8 – 15                     | dependent |          |                                  |          |

| D7      | PLLF2  | PLL Setup                       | Device    |          |                                  | 2.4.3    |

| Address<br>(hex) | Label  | Description                              | Description  Reset Value (hex)  Reset Address- able |                                  | Notes                                         | Document<br>Section |

|------------------|--------|------------------------------------------|-----------------------------------------------------|----------------------------------|-----------------------------------------------|---------------------|

|                  |        | bits 16 – 23                             | dependent                                           | dependent                        |                                               |                     |

| D9               | MCEBL  | MCE Sequencer Breakpoint<br>Address Low  | 00                                                  |                                  | Internal use                                  |                     |

| DA               | МСЕВН  | MCE Sequencer Breakpoint<br>Address High | 00                                                  |                                  | Internal use                                  |                     |

| DB               | PLLF3  | PLL Setup<br>bits 24 – 31                | Device dependent                                    |                                  |                                               | 2.4.3               |

| DC               | HWREV  | Hardware Model and Revision              | Device dependent                                    |                                  | Read only                                     | 2.4.5               |

| DD               | PLLF4  | PLL Setup<br>bits 32 – 40                | 08                                                  |                                  | IRMCF1xx<br>only                              | 2.4.3               |

| DE               | INDCOH | PLL DCO Control Word 00 (High)           |                                                     | Internal use<br>IRMCF1xx<br>only |                                               |                     |

| DF               | INDCOL | PLL DCO Control Word<br>(Low)            |                                                     |                                  | Internal use<br>IRMCF1xx<br>only              |                     |

| E0               | ACC    | Accumulator                              | 00                                                  | *                                | -                                             | 2.4.1               |

| E1               | FLDRD  | Flash Read Data                          | 00                                                  |                                  | Internal use<br>Read only<br>IRMCF1xx<br>only |                     |

| E3               | MCESL  | MCE Sequencer Stack Low                  | 00                                                  |                                  | Read only<br>Internal use                     |                     |

| E4               | MCESH  | MCE Sequencer Stack High                 | 00                                                  |                                  | Read only<br>Internal use                     |                     |

| E5               | STOPS  | GATEKILL Configuration                   | 00                                                  |                                  |                                               | 2.4.5               |

| E7               | P5     | Port 5                                   | 00                                                  | *                                |                                               | 2.4.2               |

| E8               | IE1    | Interrupt Enable Register 1              | 00                                                  | *                                |                                               | 2.5.3               |

| E9               | MCECD0 | MCE Coherent Data 0                      | 00                                                  |                                  |                                               | 4.4.1               |

| EA               | MCECD1 | MCE Coherent Data 1                      | 00                                                  |                                  |                                               | 4.4.1               |

| EB               | MCECD2 | MCE Coherent Data 2                      | 00                                                  |                                  |                                               | 4.4.1               |

| EC               | MCECD3 | MCE Coherent Data 3                      | 00                                                  |                                  |                                               | 4.4.1               |

| F0               | В      | B Register                               | 00                                                  | *                                |                                               | 2.4.1               |

| F8               | IP1    | Interrupt Priority Register 1            | 00                                                  | *                                |                                               | 2.5.4               |

**Table 5. Special Function Registers**

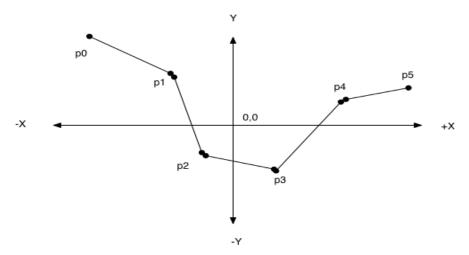

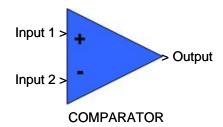

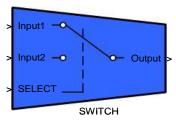

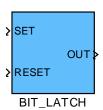

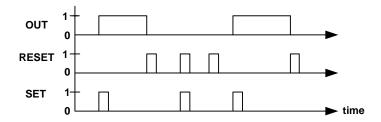

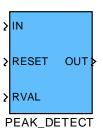

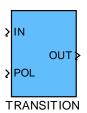

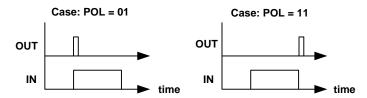

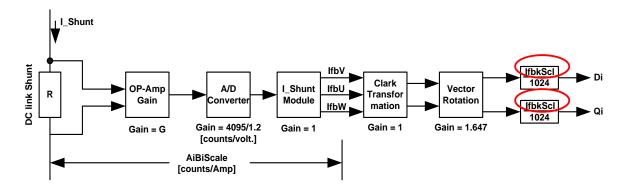

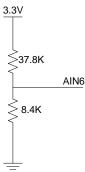

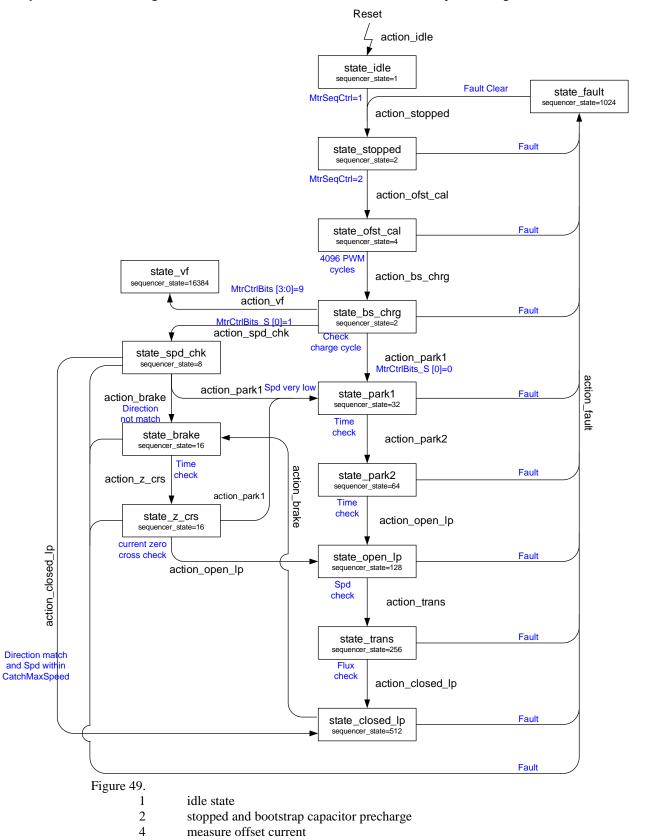

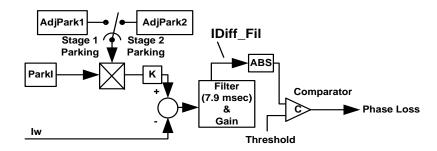

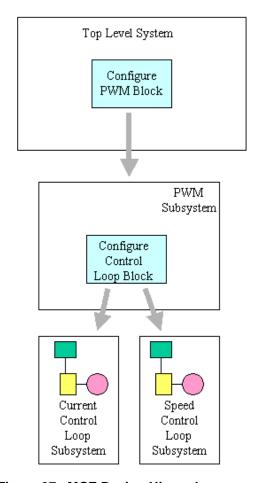

## 2.3 Peripheral Registers