# CoolSiC<sup>™</sup> MOSFET 650 V M1 trench power device

Infineon's first 650 V silicon carbide MOSFET for industrial applications

## About this document

#### Scope and purpose

Due to the worldwide increase in power consumption it is necessary to design power supplies that offer the highest possible efficiency during standard operating conditions. This application note will first give an overview covering the technological parameters of Infineon's first 650 V SiC trench MOSFET. Second, it will provide benchmarking results based on characterization data, and in target applications against competitors. Finally, it will provide design guidelines for implementing SiC in the target applications.

#### Intended audience

SMPS designers, technology developers.

Table of contents

## **Table of contents**

| About this document |                                                                                               |     |  |  |

|---------------------|-----------------------------------------------------------------------------------------------|-----|--|--|

| Table               | e of contents                                                                                 | . 2 |  |  |

| 1                   | Introduction                                                                                  | . 3 |  |  |

| 2                   | Overview of CoolSiC <sup>™</sup> M1 SiC trench power device                                   | . 4 |  |  |

| 2.1                 | Positioning                                                                                   |     |  |  |

| 2.2                 | Target applications                                                                           | 5   |  |  |

| 2.3                 | Focus topologies                                                                              |     |  |  |

| 2.3.1               | CCM totem pole PFC (or representative for any hard-switching bridge configuration)            |     |  |  |

| 2.3.2               | LLC (or representative for any resonant switching bridge configuration)                       | 8   |  |  |

| 3                   | Technology parameters                                                                         | 10  |  |  |

| 3.1                 | R <sub>DS(on)</sub> junction over-temperature                                                 | 10  |  |  |

| 3.2                 | Q <sub>rr</sub> – reverse recovery charge                                                     | 11  |  |  |

| 3.3                 | V <sub>(BR)DSS</sub> – drain-source breakdown voltage                                         | 12  |  |  |

| 3.4                 | Transfer characteristics                                                                      | 13  |  |  |

| 3.5                 | C <sub>oss</sub> – output capacitance                                                         |     |  |  |

| 3.6                 | $E_{oss}$ – energy stored in output capacitance/ $Q_{oss}$ – charge in the output capacitance |     |  |  |

| 3.7                 | V <sub>SD</sub> (V <sub>F</sub> ) – forward voltage of the body diode                         | 18  |  |  |

| 3.8                 | Q <sub>g</sub> – gate charge                                                                  | 19  |  |  |

| 4                   | Design guidelines                                                                             | 21  |  |  |

| 4.1                 | Gate driving                                                                                  | 21  |  |  |

| 4.2                 | Negative gate-source voltage                                                                  | 21  |  |  |

| 4.3                 | Kelvin source configuration                                                                   | 24  |  |  |

| 5                   | Benchmarking in target applications                                                           | 26  |  |  |

| 5.1                 | Switching energies (E <sub>on</sub> and E <sub>off</sub> )                                    | 26  |  |  |

| 5.2                 | 3.3 kW CCM totem pole PFC                                                                     |     |  |  |

| 5.3                 | 3 kW LLC converter                                                                            | 32  |  |  |

| 6                   | Summary                                                                                       | 35  |  |  |

| Revis               | ion history                                                                                   | 36  |  |  |

## 1 Introduction

The CoolSiC<sup>™</sup> MOSFET 650 V M1 trench power device is Infineon's first generation of SiC trench MOSFETs. It is designed to address the needs of power supplies in the range from several hundred watts to tens of kilowatts, including server and telecom SMPS, solar inverters and EV charging. These applications, considering the overall Total Cost of Ownership (TCO), benefit from power semiconductors and topology that serves high switching frequencies, enabling fast switching under hard-switching conditions and providing low conduction losses as well as a small output and reverse recovery charge (Q<sub>rr</sub>).

This technology enables highly efficient topologies such as the full-bridge totem pole PFC, which is by nature a bridgeless topology and therefore boosts efficiency in all load points. It can achieve peak efficiency of more than 99 percent. This high PFC efficiency is the minimum needed in order to achieve an overall system efficiency of more than 98 percent.

## 2 Overview of CoolSiC<sup>™</sup> M1 SiC trench power device

## 2.1 Positioning

Due to the CoolSiC<sup>™</sup> M1 technology parameters, which will be explained later, nearly every application/topology can benefit from it in terms of increased efficiency. Nevertheless, due to the body diode behavior and the linear output capacitance the main focus is the hard-switching topologies, which have a hard commutation on a conducting body diode in every switching cycle, e.g. in a CCM totem pole PFC, and resonant topologies like an LLC converter.

Infineon Technologies is offering Si-, SiC- and GaN-based power products. This gives customers the chance to cover the whole power transmission line from AC to DC and vice versa. Next it is necessary to explain the positioning of these three technologies.

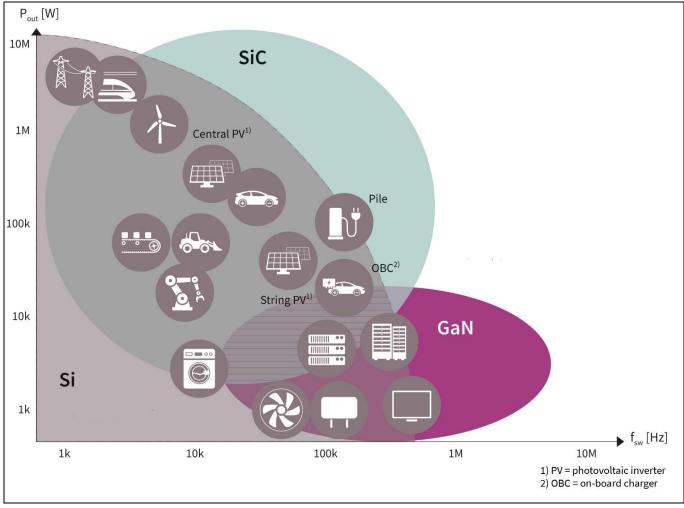

Figure 1 Positioning of Infineon technologies for HV power switches

As can be seen in the positioning diagram in Figure 1, Si power transistors will remain the mainstream technology in the next few years, covering a wide range of possible applications with adequate power and frequency possibilities. SiC, on the other hand, complements Si in many applications but also enables new solutions and topologies for higher-power and robust applications. GaN is able to achieve the highest efficiency and by nature has the best Figure-of-Merit (FOM) for achieving the highest switching frequency.

Infineon recommends the different technologies as follows:

CoolMOS<sup>™</sup>:

- Maintaining cost/performance benefit across a wide range of applications

- High efficiency (up to 97 percent) for certain power density limitations

- Easy design-in

- PFC topologies and resonant topologies covering switching frequency from 45 kHz to 300 kHz

- Short evaluation times and plenty of experience using silicon in PSU

CoolGaN<sup>™</sup>:

- Top efficiency and density: best FOM efficiency x power density

- Best for maintaining high efficiency while increasing frequency

- Totem pole PFC and any hard and resonant switching topology operating at higher frequencies

- Daughter card/SMD optimized design approach

$CoolSiC^{TM}$ :

- High efficiency and density: applications where high power is combined with high-temperature operating conditions

- Totem pole PFC and any hard and resonant switching topology

- Robustness

There is a clear overlap between the three technologies, and the selection of the right technology is heavily dependent on the application requirements, as all three technologies have a specific value proposition in the 600 V/650 V segment.

The next section of this chapter will explain the target applications and the target topologies that can benefit from SiC.

## 2.2 Target applications

With SiC MOSFETs it is possible to easily achieve the high efficiency necessary for customers in order to reduce the overall power consumption, which is dramatically increased by server, telecom and EV charging applications.

Now the question arises: why should CoolSiC<sup>™</sup> be used in the applications mentioned? This is answered in the next section.

## CoolSiC™ MOSFET 650 V M1 trench power device

#### Infineon's first 650 V silicon carbide MOSFET for industrial applications

#### Overview of CoolSiC<sup>™</sup> M1 SiC trench power device

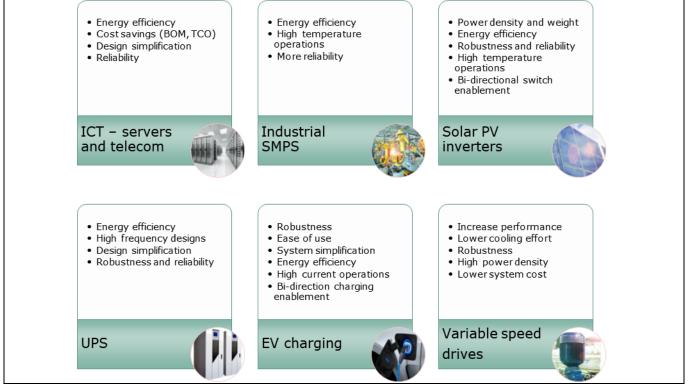

Figure 2 Target applications for CoolSiC<sup>™</sup>

In all of these applications SiC gives a high value proposition if a topology uses the internal body diode for short usage or for body diode operation in switching frequency of more than 8 kHz.

One of these topologies is the Continuous Conduction Mode (CCM) totem pole PFC, which is a bridgeless topology and by nature suitable for bi-directional operation, including highest possible efficiency compared to nearly all available PFC topologies.

## 2.3 Focus topologies

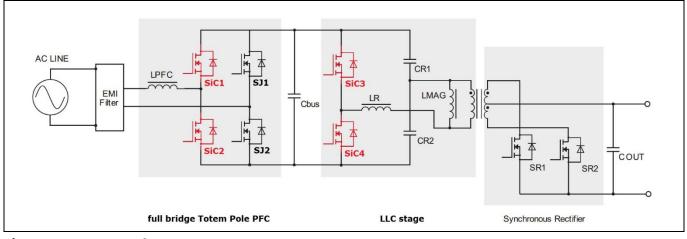

Standard server and telecom applications consist of two stages: first the AC-DC conversion, and second a DC-DC conversion as represented in the following image, based on a full-bridge CCM totem pole PFC and an LLC converter.

# 2.3.1 CCM totem pole PFC (or representative for any hard-switching bridge configuration)

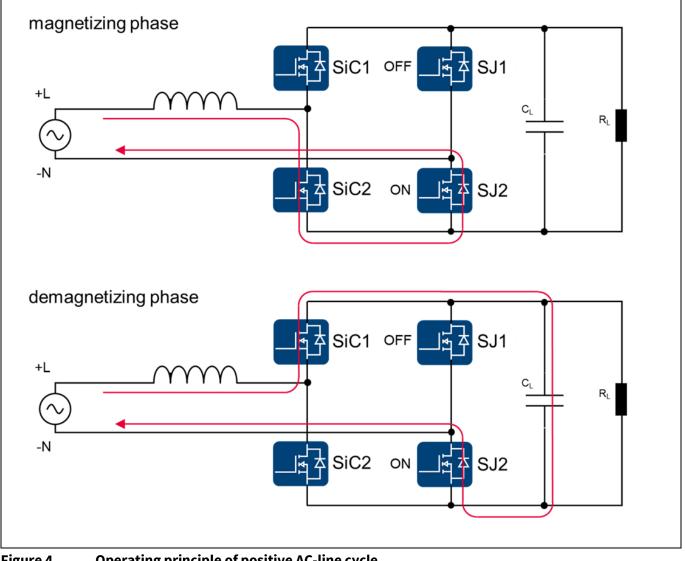

The principle of operation of the CCM totem pole PFC is simplified and divided into four phases over one AC cycle – two phases for the positive and two for the negative cycle of the input voltage.

#### Positive AC-line cycle:

The low-ohmic superjunction (SJ) MOSFET (SJ2) is continuously conducting. During the magnetizing phase the SiC MOSFET (SiC2) is turned on and operates as in a standard PFC, which is necessary in order to magnetize the PFC choke. After SiC2 is turned off, the body diode of SiC1 is conducting and finally actively turning on SiC1, and the demagnetizing phase starts. During this time SiC1 acts as a synchronous boost. At exactly the same time as the synchronous boost turns off, there is a short period in which the body diode of SiC1 is conducting again and SiC2 is actively turned on, which leads to a hard commutation on the conducting body diode. This means this hard commutation is present in every switching cycle on one of the SiC MOSFETs, and therefore the switching energy and the losses increase during this turn-on based on the  $Q_{rr}$  and the  $Q_{oss}$ .

Figure 4 Operating principle of positive AC-line cycle

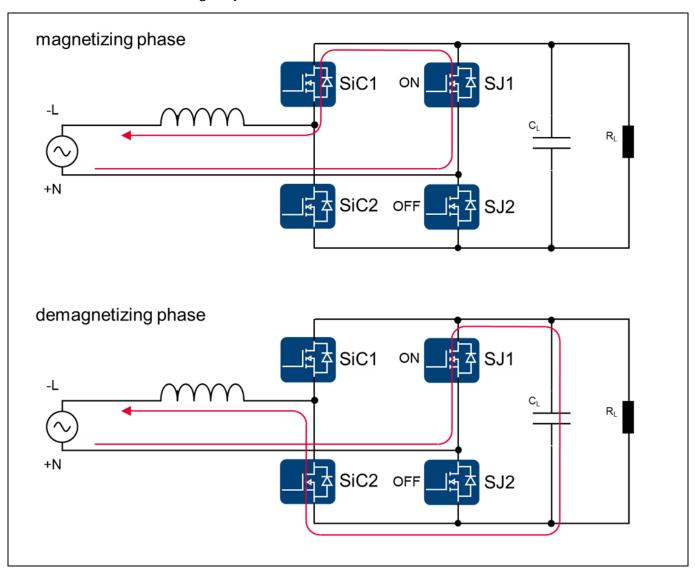

Negative AC-line cycle:

## CoolSiC<sup>™</sup> MOSFET 650 V M1 trench power device Infineon's first 650 V silicon carbide MOSFET for industrial applications Overview of CoolSiC<sup>™</sup> M1 SiC trench power device

The negative AC-line cycle operation is exactly the same as the inverted positive AC-line cycle. In this case the low-ohmic SJ MOSFET (SJ1) is continuously conducting. During the magnetizing phase the SiC MOSFET (SiC1) is turned on and operates as in a standard PFC, which is necessary in order to magnetize the PFC choke. After SiC1 is turned off, the body diode of SiC2 is conducting and finally actively turning on SiC2, and the demagnetizing phase starts. During this time SiC2 acts as a synchronous boost. As can be seen in this topology, the already mentioned lowest possible Q<sub>rr</sub> and Q<sub>oss</sub> are required, as during every switching cycle there is a hard commutation on the conducting body diode.

Figure 5 Operating principle of negative AC-line cycle

For this reason the SiC MOSFET and its related technology parameters are the optimum choice to easily achieve 99 percent efficiency.

## 2.3.2 LLC (or representative for any resonant switching bridge configuration)

Due to the low Q<sub>rr</sub> and Q<sub>oss</sub> CoolSiC<sup>™</sup> can give the system on the one hand an increased system reliability in abnormal operating conditions, and fast changes in switching frequency due to e.g. load jumps, and on the other hand higher efficiency and the possibility to boost the switching frequency due to easily achievable full Zero Voltage Switching (ZVS) under any load condition and/or reduction of the resonant current in order to achieve full ZVS operation.

#### Overview of CoolSiC<sup>™</sup> M1 SiC trench power device

The next chapter describes the CoolSiC<sup>™</sup> technology parameters compared to the most well-known technology, CFD7, before looking at the results in the application testing.

Technology parameters

## **3** Technology parameters

This chapter will describe the most important technology parameters and give general recommendations for using CoolSiC<sup>™</sup>.

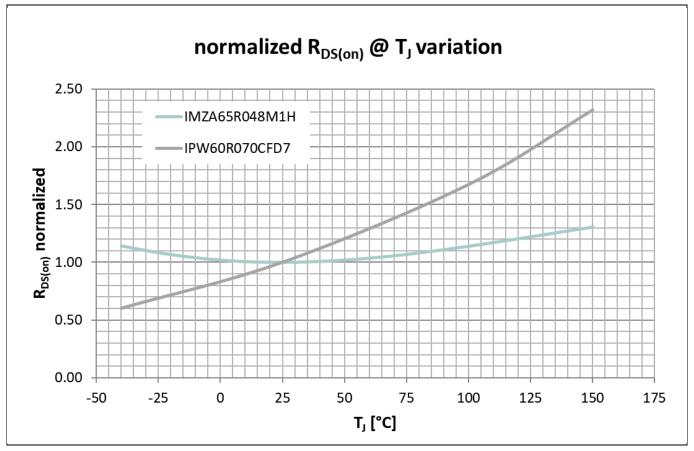

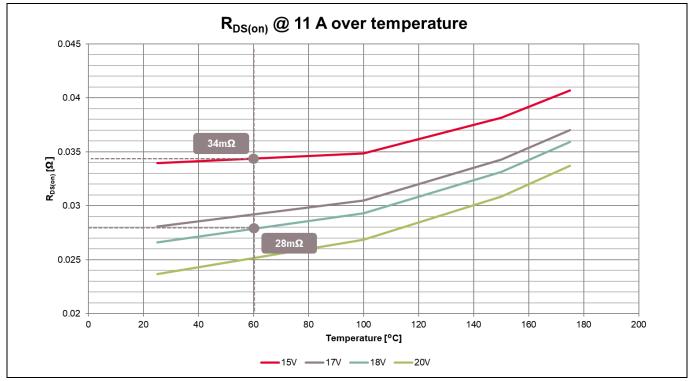

## 3.1 R<sub>DS(on)</sub> junction over-temperature

One of the most important benefits of CoolSiC<sup>TM</sup> describes the thermal characteristics of the on-state resistance. In all device datasheets the typical  $R_{DS(on)}$  is represented at 25°C junction temperature. Usually the devices operate at higher junction temperatures, so it is also necessary to know the  $R_{DS(on)}$  at higher temperatures, for example at 100°C.

The junction temperature can be seen on the X-axis, and on the Y-axis the normalized  $R_{DS(on)}$  is visible. The gray line correlates to the CoolMOS<sup>TM</sup> and the blue line to the CoolSiC<sup>TM</sup> devices. It is shown that at 25°C the  $R_{DS(on)}$  is the same for CoolMOS<sup>TM</sup> and CoolSiC<sup>TM</sup>. This 25°C value is represented in the datasheets and in the naming convention.

Figure 6Normalized  $R_{DS(on)}$  over-temperature comparison between CoolMOS<sup>TM</sup> and CoolSiC<sup>TM</sup>

The multiplication factor from 25°C to 100°C to the  $R_{DS(on)}$  is 1.67 for CoolMOS<sup>TM</sup> and 1.13 for CoolSiC<sup>TM</sup>. This means that in order to have the same conduction losses ( $P_{cond} = I^2 \cdot R_{DS(on)}(T_J)$ ) of CoolMOS<sup>TM</sup> and CoolSiC<sup>TM</sup> it is possible to design-in a higher  $R_{DS(on)}$  for CoolSiC<sup>TM</sup>. Ideally there is the potential for CoolSiC<sup>TM</sup> 84 m $\Omega$  to have the same conduction losses as a 57 m $\Omega$  CoolMOS<sup>TM</sup> at 100°C. Beside of the same conduction losses, CoolSiC<sup>TM</sup> also enables lower switching losses and lower cost.

**Technology parameters**

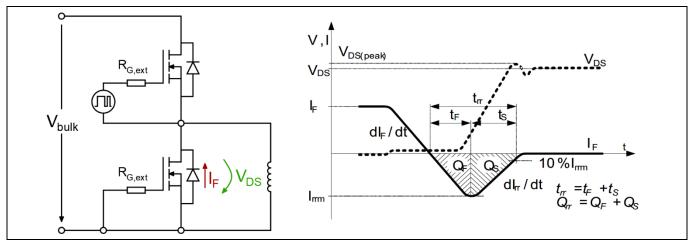

## 3.2 Q<sub>rr</sub> – reverse recovery charge

As already anticipated, the reverse recovery charge  $(Q_{rr})$  is one of the most important parameters for any resonant topology, or any topology that has a continuous hard commutation on a conducting body diode. Such a topology is the already explained CCM totem pole PFC. The  $Q_{rr}$  is the charge that needs to be removed from the body diode after it is conducting. In the diagram the  $Q_{rr}$  is shown as the area below the 0 A line.

**Figure 7** Simplified explanation for Q<sub>rr</sub> measurement

CoolMOS<sup>™</sup> has already found ways to improve or reduce the Q<sub>rr</sub> of the body diode, which came out as a fast diode device like the CFD or CFD7. Nevertheless, this charge is still too much in order to achieve high efficiency values in the CCM totem pole PFC, but now the CoolSiC<sup>™</sup> can be used. CoolSiC<sup>™</sup> has 10 times lower charge than the best fast diode SJ MOSFET available on the market.

Figure 8  $Q_{rr}$  comparison between CoolMOS<sup>TM</sup>, CoolMOS<sup>TM</sup> fast diode and CoolSiC<sup>TM</sup>

#### **Technology parameters**

It is only because of this behavior that CoolSiC<sup>™</sup> is able to achieve more than 99 percent peak efficiency in the PFC stage.

## 3.3 V<sub>(BR)DSS</sub> – drain-source breakdown voltage

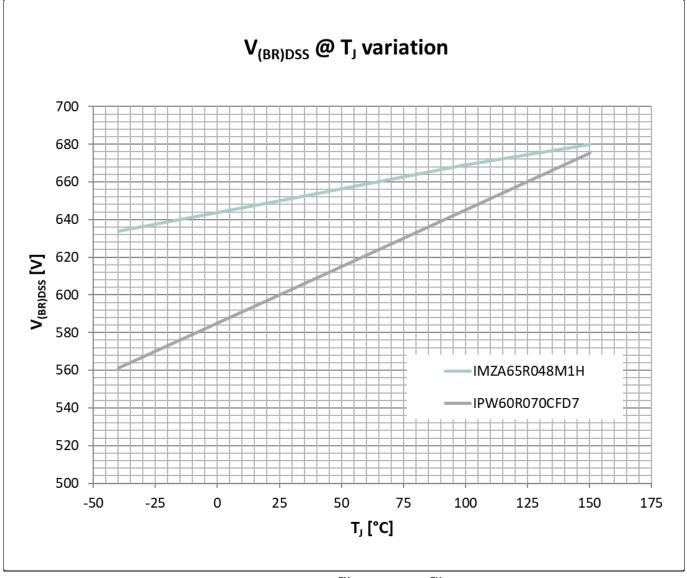

In general the behavior of the breakdown voltage from CoolSiC<sup>™</sup> and CoolMOS<sup>™</sup> is equal; the main difference is that CoolSiC<sup>™</sup> has a lower slope, as can be seen in Figure 9, in which the X-axis corresponds to the junction temperature and the Y-axis represents the breakdown. One very important difference is that at lower temperatures the breakdown voltage is higher than compared to CoolMOS<sup>™</sup>, which is beneficial for customers for outdoor applications or applications that start up at lower temperatures. CoolSiC<sup>™</sup> has a rated breakdown voltage of 650 V at 25°C for the whole portfolio.

Figure 9 V<sub>(BR)DSS</sub> comparison between CoolMOS<sup>™</sup> and CoolSiC<sup>™</sup>

It is never recommended to apply voltages above the rated breakdown voltage even during switching transients and abnormal operation conditions.

Technology parameters

## 3.4 Transfer characteristics

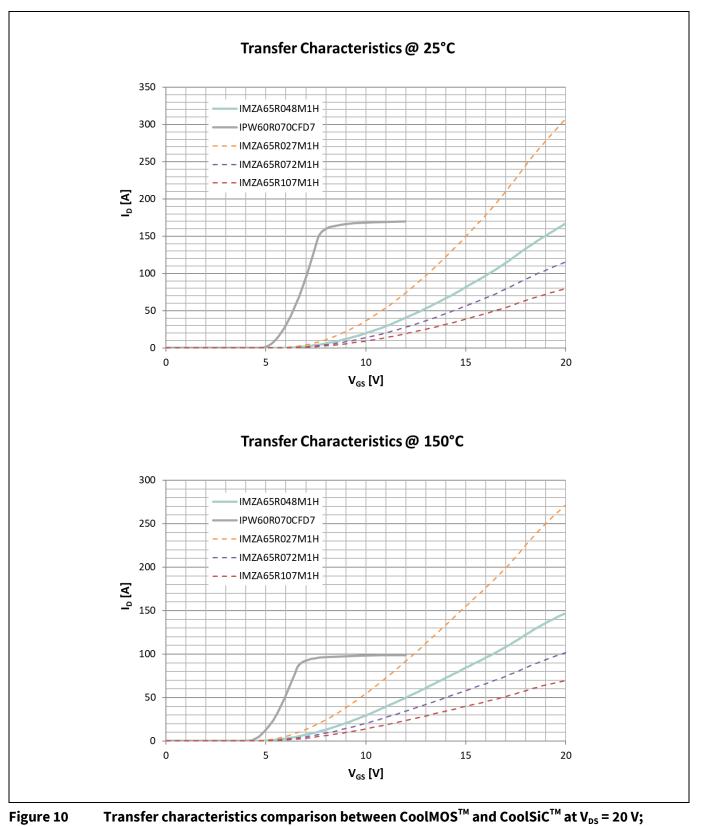

This technology parameter is very important as it describes how much current can be transferred via the channel and the dependency on the gate-source voltage.

$T_{J} = 25^{\circ}C$  (upper) and  $T_{J} = 150^{\circ}C$  (lower)

**Technology parameters**

In these two graphs the X-axis describes the gate-source voltage and the Y-axis the transferable drain current. The straight gray line represents the CoolMOS<sup>™</sup> and the straight blue line the CoolSiC<sup>™</sup> device. The dashed lines always represent the different  $R_{DS(on)}$  classes of CoolSiC<sup>TM</sup>. The additional lines are included in all technology parameters due to the R<sub>DS(on)</sub> over-temperature behavior. The upper graph shows the transfer characteristics at 25°C and the lower graph shows them at 150°C.

As can be seen, the transfer characteristics here also follow the same basic principles. Nevertheless, CoolSiC<sup>™</sup> shows up to 20 V gate-source voltage with no saturation, unlike CoolMOS<sup>™</sup>, which saturates at around 10 V. It is also clear to see why for CoolSiC<sup>™</sup> the 18 V driving voltage is recommended in order to enable driving the current required by the application. This does not mean that CoolSiC<sup>™</sup> cannot be driven with lower gate-source voltage - it absolutely can - but customers need to consider which drain current they need in their application and not operate it in linear mode.

Another very important benefit of CoolSiC<sup>™</sup> is again visible due to the R<sub>DS(on)</sub> over-temperature behavior; the transfer characteristics show nearly no impact at 150°C. This means that at 25°C ideally CoolMOS<sup>™</sup> can transfer higher currents, but the higher the temperature gets the worse is the behavior of CoolMOS<sup>™</sup> in comparison to CoolSiC<sup>™</sup>.

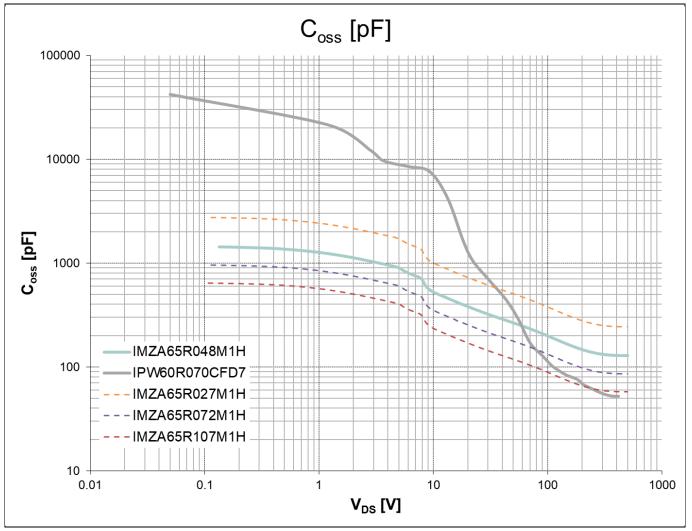

#### Coss - output capacitance 3.5

The output capacitance for both technologies as it is a very important indicator with respect to switching speed and EMI behavior. In this graph it is visualized that CoolMOS<sup>™</sup> CFD7 offers much lower output capacitance than CoolSiC<sup>™</sup> with the same typical R<sub>DS(on)</sub> at 25°C above 50 V drain-source voltage.

#### **Technology parameters**

Figure 11 Typical  $C_{oss}$  of CoolMOS<sup>TM</sup> and CoolSiC<sup>TM</sup>

This indicates that  $CoolMOS^{TM}$  has the capability to offer lower  $E_{oss}$ , which is the energy stored in the output capacitance that needs to be dissipated during a non-zero-voltage turn-on, allowing for higher switching speed and lower switching losses. However, lower output capacitance at higher voltages may lead to a higher sensitivity of PCB behavior and design parasitics, including drain-source voltage overshoots during turn-off, resulting in higher  $R_G$  usage for  $CoolMOS^{TM}$ . At voltages below 50 V drain-source voltage,  $CoolSiC^{TM}$  offers lower capacitances than  $CoolMOS^{TM}$ , therefore representing a much more linear output capacitance behavior. A higher output capacitance at higher voltages does not directly mean there is no benefit from this capacitance.

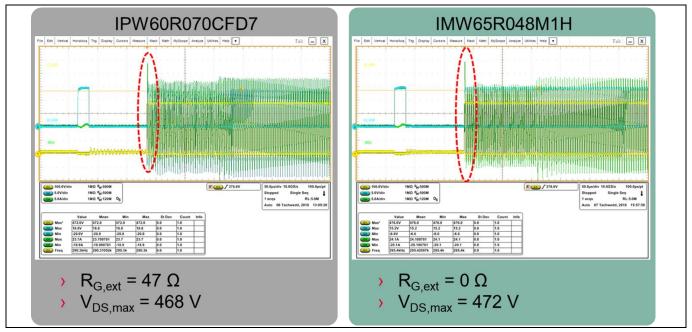

The benefit of a higher  $C_{oss}$  at higher voltages is directly interlinked with the "ease of use" in target applications and a direct indicator for the switching losses. In Figure 12 a comparison in the same 3 kW LLC converter during start-up is shown. The marked waveform is the drain-source voltage peak. It can be clearly seen that due to the higher output capacitance the CoolSiC<sup>TM</sup> does not need to be manually slowed down via the external gate resistor in order to stay within de-rating guidelines of 80 percent V<sub>DS,max</sub>.

#### Technology parameters

Figure 12 V<sub>DS</sub> overshoot during start-up in 3 kW LLC converter

Typically, customers are used to 80 percent de-rating on the drain source voltage, which means that the maximum allowed drain-source voltage peak is 80 percent of the rated blocking voltage in the datasheets. In order to have this de-rating guideline applied it is necessary to manually slow down the switching speed of the CoolMOS<sup>TM</sup> with an external turn-on gate resistor of 47  $\Omega$ . Meanwhile, on the right-hand side the external gate resistor for CoolSiC<sup>TM</sup> is adjusted to 0  $\Omega$  while still having more than 80 percent de-rating. This external gate resistor has a big impact on the switching losses during turn-off, especially if the turn-off current is increased.

As result CoolSiC<sup>™</sup> offers much greater ease-of-use with respect to voltage peaks.

Based on the  $C_{oss}$  the next two parameters can be directly derived from this parameter.

# 3.6 E<sub>oss</sub> – energy stored in output capacitance/Q<sub>oss</sub> – charge in the output capacitance

The E<sub>oss</sub> is derived by:

$$E_{oss} = \int_{0}^{400 V} C_{oss} \cdot V \, dV$$

and the  $Q_{oss}$  by:

$$Q_{oss} = \int_{0}^{400 V} C_{oss} \cdot \frac{\mathrm{dV}}{\mathrm{dt}} \,\mathrm{dt}$$

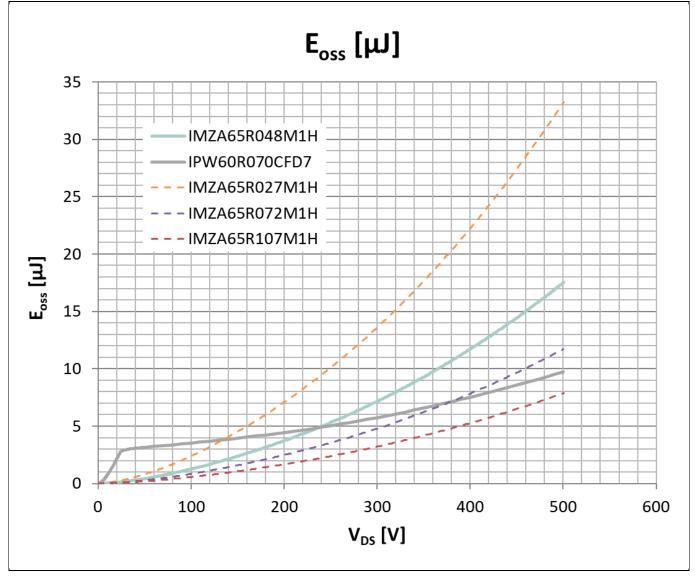

The following diagram illustrates the  $E_{oss}$  in  $\mu J$  on the Y-axis and the related drain-source voltage on the X-axis. Due to the higher output capacitance at voltages above 50 V also the related the energy stored in the output capacitance which needs to be dissipated during a non-zero-voltage turn-on is 400 V higher than the CoolMOS<sup>TM</sup> counterpart compared to the same typical  $R_{DS(on)}$ . This leads to the assumption that the hard-switching turn-on losses at 400 V bulk voltage are around 1.5 times higher than CoolMOS<sup>TM</sup>. Despite this fact, the  $E_{oss}$  is much smaller than the real turn-on losses in a CCM totem pole PFC, as this also depends on the  $Q_{oss}$  and the  $Q_{rr}$  of the

#### **Technology parameters**

devices. It can also be seen that using the  $R_{DS(on)}$  over-temperature benefit from CoolSiC<sup>TM</sup> and comparing the 72 m $\Omega$  against the CoolMOS<sup>TM</sup> counterpart the  $E_{oss}$  drawback is once again on the same level.

Figure 13  $E_{oss}$  comparison between CoolMOS<sup>TM</sup> and CoolSiC<sup>TM</sup>

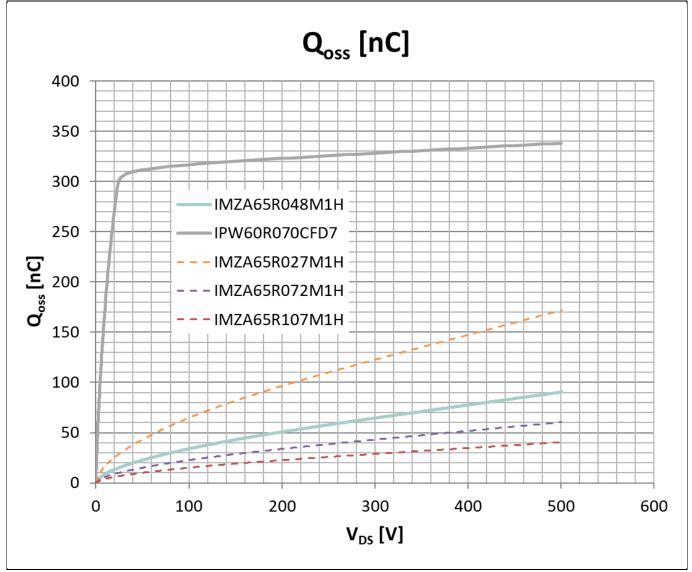

As already anticipated,  $CoolSiC^{TM}$  can be used in the high-efficiency CCM totem pole PFC, while  $CoolMOS^{TM}$  cannot. This technology parameter is one key parameter which makes this possible. During hard commutation on a conducting body diode the  $Q_{oss}$  also needs to be discharged accordingly, leading to additional losses. In this case the  $CoolSiC^{TM}$  offers around 75 percent lower  $Q_{oss}$  at 400 V.

#### Technology parameters

Figure 14 Q<sub>oss</sub> comparison between CoolMOS<sup>™</sup> and CoolSiC<sup>™</sup>

This difference arises from the linear output capacitance of  $CoolSiC^{TM}$ . Especially in the region of less than 50 V drain-source voltage the  $CoolMOS^{TM}$  has one or two orders of magnitude higher  $C_{oss}$ , resulting in a big step of the  $Q_{oss}$ . The  $Q_{oss}$  is also related in resonant topologies that define the current and time, which is necessary in order to achieve full ZVS operation. As the charge is described by current multiplied by time designers can reduce either the necessary recirculating current or the time resulting on one side on the reduced losses, and on the other side there is the possibility to increase switching frequency.

There is one drawback for CoolSiC<sup>TM</sup> related to the lower  $Q_{oss}$  and the body diode, which will be described in the following section.

## 3.7 $V_{SD}(V_F)$ – forward voltage of the body diode

As already visible in the Q<sub>rr</sub> analysis, the body diode of CoolSiC<sup>™</sup> shows ruggedness never seen before in any silicon counterpart. Nevertheless, the forward voltage is around four times higher than the body diode of a CoolMOS<sup>™</sup>.

#### **Technology parameters**

| Table 1Forward voltage co                                | e 1 Forward voltage comparison between IMZA65R048M1H and IPW60R070CF |          |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------|----------|--|--|--|

| Parameter                                                | CoolSiC™                                                             | CoolMOS™ |  |  |  |

| V <sub>F,typical</sub> at I <sub>F</sub> = 15 A and 25°C | 3.6 V                                                                | 1 V      |  |  |  |

This leads to the fact, that if customers intend to use the CoolSiC<sup>™</sup> in a plug-and-play scenario without adapting or reducing the body diode conduction time, the body diode conduction losses will be around four times higher at the same diode current. This can impact the light load efficiency in an LLC converter depending on the output power up to 0.5 percent, which will be described in the benchmark section of this application note. A very important point is also that in order to achieve the highest possible peak efficiency in a CCM totem pole PFC, it is necessary to boost via the channel and not the body diode.

#### 3.8 Q<sub>G</sub> – gate charge

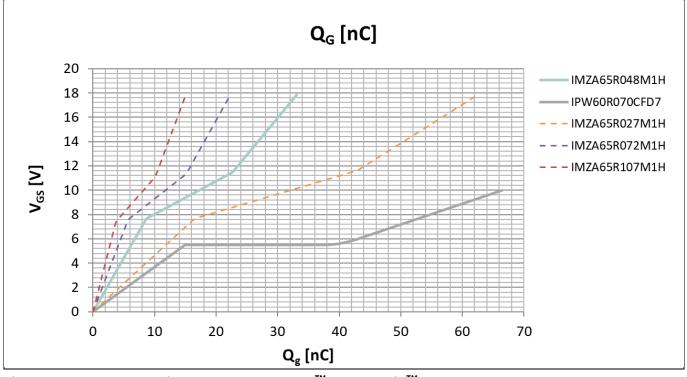

The final technology parameter is the gate charge. The gate charge is an indicator of how quickly a device can be turned on and off. Furthermore, it describes the charge needed in order to fully activate the device, resulting in an indicator for switching losses.

The diagram shows the gate charge on the X-axis and the gate-source voltage on the Y-axis. In this comparison it can be seen that the CoolSiC<sup>™</sup> has around 50 percent lower gate charge in order to turn on the device with the same typical R<sub>DS(on)</sub>.

$\boldsymbol{Q}_{\boldsymbol{G}}$  comparison between CoolMOS^M and CoolSiC^M Figure 15

CoolMOS<sup>™</sup> has a clear plateau visible, which is the so-called Miller plateau derived from the Miller capacitance, also known as gate-drain capacitance C<sub>GD</sub>. CoolSiC<sup>™</sup> does not show a plateau like CoolMOS<sup>™</sup>, which is the socalled Drain Induced Barrier Lowering (DIBL) where the electric field from the drain of the chip starts to act on the channel by depleting it. In the DIBL  $V_{\mbox{\scriptsize GS(th)}}$  decreases with increasing drain-source voltage.

C<sub>GS</sub> is still being charged during this Miller plateau. With the opening channel, e.g. decreasing V<sub>DS</sub>, more and more charges in the channel have to be controlled by the gate, so they contribute to charging the C<sub>GS</sub>. In long-

#### **Technology parameters**

channel devices such as the CoolMOS<sup>™</sup> the plateau is flat, because all charges in the channel are independent of the V<sub>DS</sub>; for example, they are always completely controlled by the gate electrode. So once the channel is open, the gate electrode must provide charges for C<sub>GD</sub> (which is changing because of the drift zone filling with mobile carriers), but not for C<sub>GS</sub>, hence the plateau.

Now that the technology differences are known, the following section will focus on some application-related guidelines and also some application benchmarks.

4 Design guidelines

The first guideline will describe the positive and negative aspects related to the gate driving.

## 4.1 Gate driving

One of the benefits of this Wide Bandgap (WBG) technology is the possibility of using standard gate drivers like CoolMOS<sup>™</sup>, as it is operating is the same way. Nevertheless, customers should consider one very important factor: Infineon recommends a driving voltage from 0 V to 18 V.

In general, customers should not use negative gate driving – this will be explained later in this document. The 18 V gate driving can be very beneficial to the customer, as there is the chance to reduce the  $R_{DS(on)}$  by around 18 percent if not using 15 V. CoolSiC<sup>TM</sup> can also be driven at lower voltages like CoolMOS<sup>TM</sup>; nevertheless, the  $R_{DS(on)}$  will have a negative effect when operating in this condition.

Figure 16 R<sub>DS(on)</sub> dependency on V<sub>GS</sub>

This diagram clearly describes the  $R_{DS(on)}$  dependency of the gate voltage. On the Y-axis the  $R_{DS(on)}$  is represented in absolute values. On the X-axis the junction temperature is visible. Comparing the  $R_{DS(on)}$  with the 15 V gatesource voltage, the red line and the 18 V gate-source voltage, and the light blue line at 60°C, it is possible to see that the  $R_{DS(on)}$  changes from 34 m $\Omega$  to 28 m $\Omega$ , which can have a big impact, especially under full-load condition.

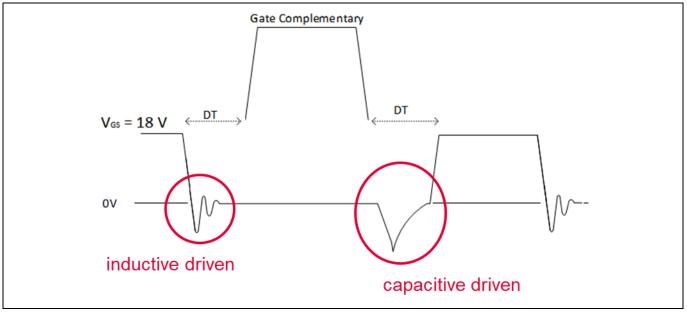

## 4.2 Negative gate-source voltage

Now to explain the negative gate-source voltage. Negative gate-source voltage can have two root causes. First of all, the inductive-driven gate-source voltage oscillation during turn-off, which is mainly driven by turning off at high di/dt, which generates a voltage drop over the source inductance inside the gate-drive loop.

Design guidelines

The second root cause is the capacitive-driven negative gate-source voltage, which is coupled via the  $C_{GD}$  of the MOSFET by having high dv/dt transients from the second switch in a half-bridge configuration. For both of these root causes, there are ways to improve or reduce the effect on the gate, but before starting to explain the solution the impact needs to be clarified.

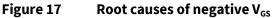

Negative gate-source voltages below -2 V can influence the threshold voltage and the resulting  $R_{DS(on)}$  over the lifetime, depending on operation frequency, duration and amplitude of the negative voltage. The 650 V CoolSiC<sup>TM</sup> was performing a long-term test in the target application with the following test parameters.

Figure 18 Test parameters to see the impact of negative V<sub>GS</sub> in the CCM totem pole PFC

After applying these test parameters, characterization of the devices used and using a calculation model we observed a threshold voltage increase by 600 mV, which results in an  $R_{DS(on)}$  increase of 8 percent after 15 years. This additional  $R_{DS(on)}$  after 15 years of life is implemented in the maximum  $R_{DS(on)}$  rating in the final datasheets. For more information about this phenomenon please refer to application note <u>AN2018-09</u>.

As the root causes and the effect are described, the solutions to these challenges also need to be discussed. The capacitive-driven negative gate-source voltage was seen as the greatest challenge, as it has the highest impact on the drift. One solution for both root causes is to manually reduce the di/dt and dv/dt, but this would result in increased switching losses and therefore reduced efficiency, so this solution will not be described further.

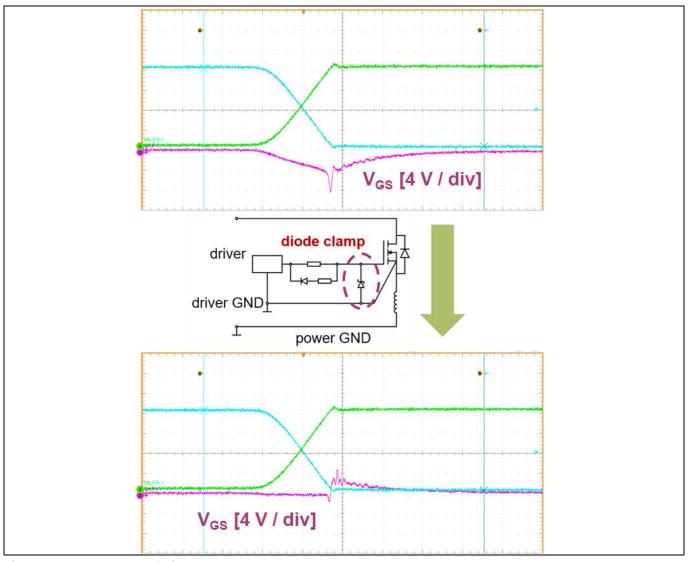

The use of a diode clamp can be the solution for both the capacitive- and inductive-driven root cause, and is the recommended solution. In these two waveforms the gate-source voltage is shown, and it is possible to directly see that there is no  $V_{GS}$  lower than -2 V and therefore no  $V_{GS(th)}$  drift. It is very important that the diode is located close to the power device.

Figure 19 Impact of diode clamp

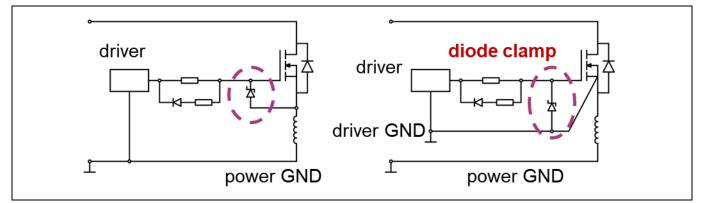

For the inductive-driven root cause the source impedance in the gate-drive loop can be reduced by splitting the common source to a power source and driver source concept, which is represented in the two simplified circuits. In these conditions there is now high di/dt, as shown by the gate during turn-off and therefore not under-voltage peak. Figure 20 describes the simplified circuits for a standard source connection, the Kelvin source connection and the diode gate clamp. Therefore, in order to reduce unwanted re-turn-on the driver needs to be placed as close as possible to the power device.

#### Design guidelines

Please be aware also that the parasitic gate inductance can have an impact on the negative  $V_{GS}$ . The Kelvin source configuration applies an additional benefit, which is described next.

## 4.3 Kelvin source configuration

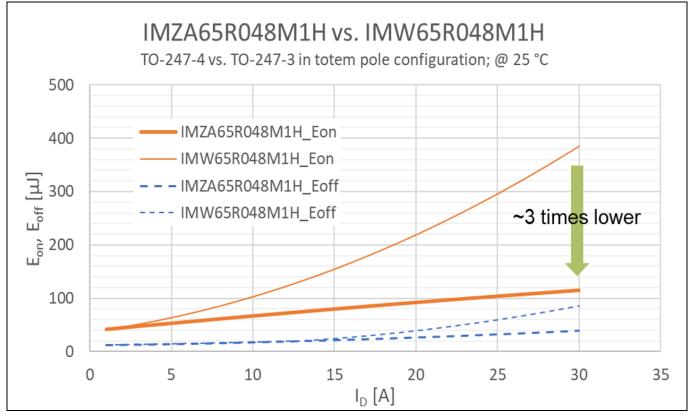

Infineon Technologies has been offering products with Kelvin source connection for years, as Infineon really wants to achieve the best efficiency and performance in customer applications. Figure 21 shows the impact of the Kelvin source with respect to the switching losses  $E_{on}$  and  $E_{off}$  on the Y-axis over the drain current on the X-axis. Especially in a totem pole configuration, the  $E_{on}$  values are the point of interest.

Figure 21 Comparison of switching energies of standard and Kelvin source configuration

In a 3.3 kW totem pole PFC at a 90-degree phase angle, the turn-off current reaches around 25 A to 30 A. As can be seen, the E<sub>on</sub> losses of this device are heavily dependent on the drain current. The higher the current, the greater the benefit for the designer with respect to switching losses. With the conditions mentioned there are

#### **Design guidelines**

up to three times lower switching losses. Assuming an average 13 A at 3.3 kW over the AC cycle and 65 kHz switching frequency this results in 3.9 W, which must additionally be dissipated over one MOSFET only due to switching losses.

As the overall CoolSiC<sup>™</sup> technology is very similar to CoolMOS<sup>™</sup> with respect to usage, all other restrictions are valid for both technologies and are therefore not described further in this document.

Benchmarking in target applications

## 5 Benchmarking in target applications

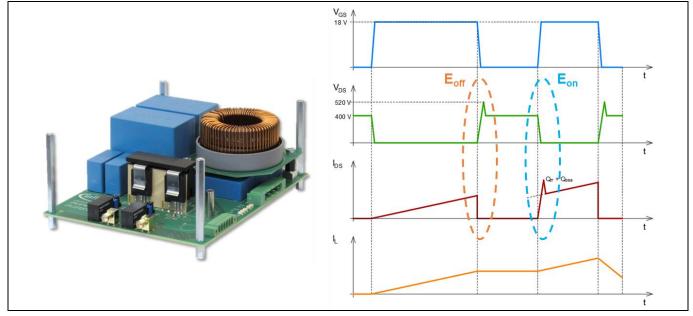

As already anticipated this application note will first start to show  $E_{on}$  and  $E_{off}$  measurements of CoolSiC<sup>TM</sup> for the different  $R_{DS(on)}$  classes. It is always very important to mention the  $E_{on}$  and  $E_{off}$  values, which are heavily dependent on the measurement set-up due to parasitic inductances, coupling capacitors, gate-drive loop, operating conditions and more. Therefore, these values are not implemented in CoolSiC<sup>TM</sup> datasheets, as the values probably do not represent the behavior in end customer designs.

## 5.1 Switching energies (E<sub>on</sub> and E<sub>off</sub>)

The represented data is measured in the following set-up:

Figure 22 Test set-up for E<sub>on</sub> and E<sub>off</sub> measurements (double-pulse set-up)

As can be seen, the  $E_{on}$  values include the losses related to the hard commutation on a conducting body diode, which represents the standard operation in a CCM totem pole PFC. For further information related to the measurement set-up please see application note <u>AN2017-44</u>.

With this test set-up it is possible to test IGBT and CoolSiC<sup>™</sup> up to 900 V bulk voltage, and it is also suitable for 400 V bulk voltage and the assessment of switching losses of the 650 V CoolSiC<sup>™</sup>.

The results represented will show the 27 m $\Omega$ , 48 m $\Omega$  and 72 m $\Omega$  typical R<sub>DS(on)</sub>, launched in February 2020.

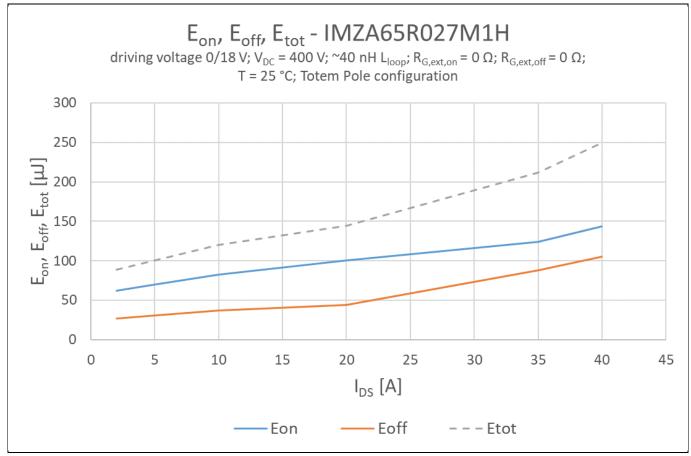

Figure 23 Typical switching energies for IMZA65R027M1H

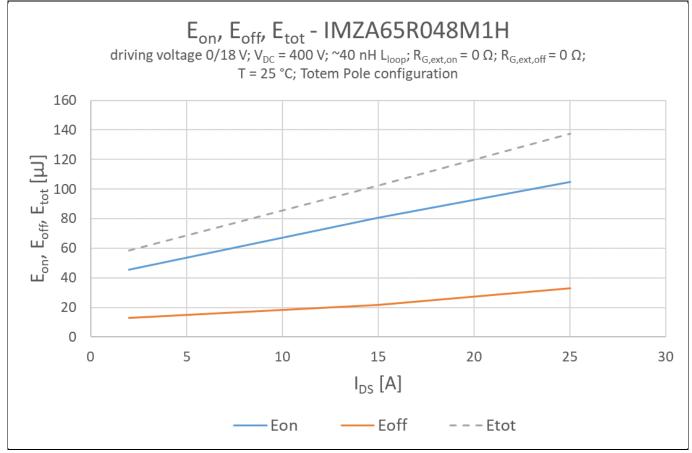

Figure 24 Typical switching energies for IMZA65R048M1H

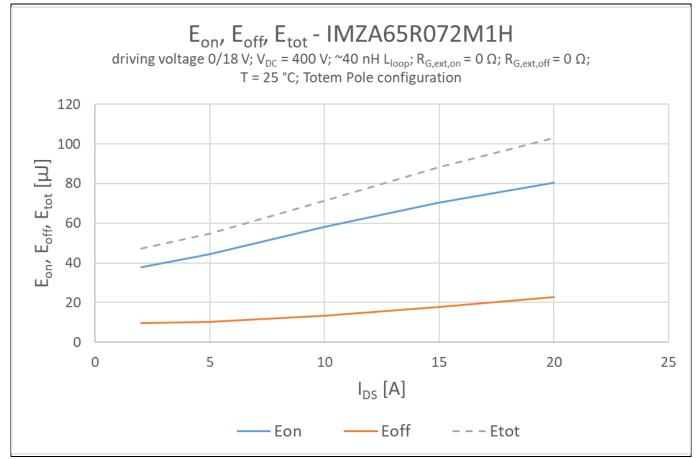

Figure 25 Typical switching energies for IMZA65R072M1H

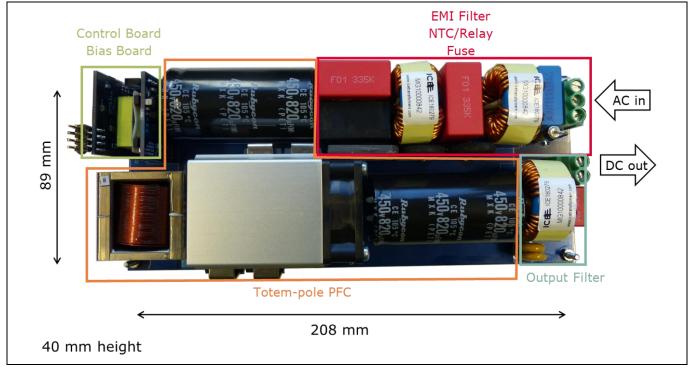

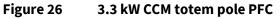

## 5.2 3.3 kW CCM totem pole PFC

The CCM totem pole PFC is the highest-efficiency bridgeless topology, achieving efficiency higher than 99 percent peak. 99 percent efficiency is necessary to achieve system efficiency of an SMPS of above 98 percent. This power supply is a 3.3 kW server power supply, a full Infineon solution using the IMZA6R048M1H as boost stage including 600 V CoolMOS<sup>™</sup> C7 17 mΩ devices as grid rectifier, Infineon 18 V auxiliary bias supply, XMC1404 and more. The input voltage is from 176 V AC to 360 V AC, fully capable of 3.3 kW output power at 400 V output voltage and a switching frequency of 65 kHz. This board can also be equipped with the newest static switch from Infineon technologies, the 600 V CoolMOS<sup>™</sup> S7.

neon

#### Benchmarking in target applications

Figure 27 shows the absolute efficiency over the output power at 230 V AC input voltage and 25°C ambient temperature, which was possible to achieve with the IMZA65R048M1H. The gray line corresponds to the IMZA65R048M1H, which has more than 99 percent from 20 percent to 50 percent of load. Even with the IMZA65R072M1H it is possible to achieve 99 percent peak efficiency and full capability to deliver the output power down to 176 V AC. Also the IMZA65R107M1H is able to come close to 99 percent peak efficiency and can operate up to 3.3 kW at 230 V AC; nevertheless, by decreasing the input voltage the output power also needs to be reduced due to thermal management. If the customer is willing to reduce the output power at lower input voltages it can lower costs significantly.

Figure 27 Efficiency comparison between CoolMOS<sup>™</sup> and CoolSiC<sup>™</sup>

The best calculated efficiency which can be achieved in a dual-boost PFC by CoolMOS<sup>™</sup> is represented as a green line with a peak efficiency of 98.85 percent; nevertheless, this might result in an increased Bill of Materials (BOM) cost due to the use of a synchronous grid, additional magnetics and space restrictions. It would be possible to further improve the efficiency using CoolMOS<sup>™</sup> in a TCM totem pole PFC; this would result in much higher driving and controlling complexity, and once again a higher part count.

All restrictions on V<sub>GS</sub> and 80 percent de-rating on V<sub>DS</sub> are applicable for CoolSiC<sup>™</sup>, and the best measurement results in this design are obtained by the following external gate resistor selection.

| Table 2 | Used R <sub>G,ext</sub> values for the 3.3 kW CCM totem pole PFC |

|---------|------------------------------------------------------------------|

|---------|------------------------------------------------------------------|

| Device        | R <sub>G,ext</sub> [Ω] |

|---------------|------------------------|

| IMZA65R048M1H | 6.4                    |

| IMZA65R072M1H | 10                     |

| IMZA65R107M1H | 15                     |

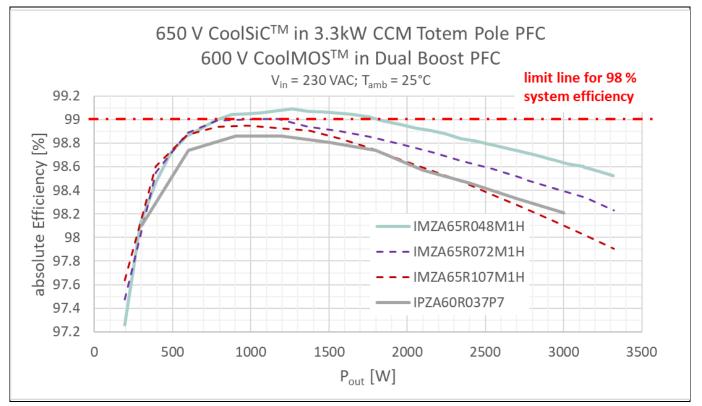

In order to operate the IMZA65R107M1H at lower input voltages and benefit from lower costs in a CCM totem pole PFC it is necessary to reduce the output power based on the decreased input voltage. According to this measurement the mold compound temperature was kept constant at 80°C at 25°C ambient.

ineor

Figure 28 Power de-rating need for low V<sub>in</sub> for IMZA65R107M1H

In order to verify that the junction temperature is not exceeding the limit in the datasheet at 60°C ambient the assumption based on simulations is taken that the junction in this system has around 20°C higher temperature than the mold compound. Under these conditions there is still enough safety margin. It can be clearly seen that it is possible to have full output power down to 220 V AC. Further increasing the input voltage leads to an output power de-rating down to 2.5 kW at 176 V AC input voltage.

## 5.3 3 kW LLC converter

Due to the described technology parameters CoolSiC<sup>™</sup> is also a very good fit for resonant topologies like the LLC converter. The body diode behavior can improve the system stability under certain operating conditions in which a hard commutation can occur.

This test board is based on telecom requirements with an input voltage of 380 V DC and an output power of 3 kW at 54 V output voltage. For the measurements only one rail of the dual phase was chosen in order to see the differences on the primary-side MOSFETs while not depending on the synchronous rectification on the secondary stage.

#### Benchmarking in target applications

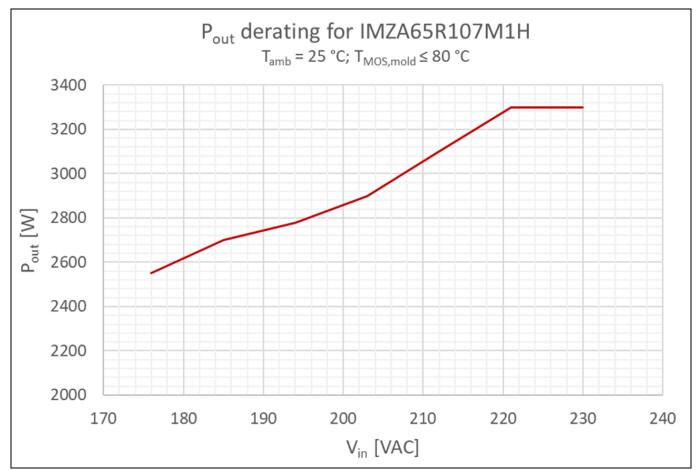

Figure 29 Relative efficiency comparison with optimized body diode conduction time

This set-up was introduced with CoolMOS<sup>™</sup>, and so the measurements can only show a comparison with maximum 14 V gate driving.

The diode conduction times of silicon carbide devices have been measured. From this, the diode losses have been calculated and implemented in the efficiency curves in order to get an estimation of the resulting efficiency in case optimized dead-times were used. This calculation has not been done for CoolMOS<sup>™</sup> devices, since diode conduction time – due to non-optimal dead-times – is an almost-negligible contribution to the overall efficiency. With these considerations, CoolSiC<sup>™</sup> can have around 0.5 percent higher efficiency, especially at light load.

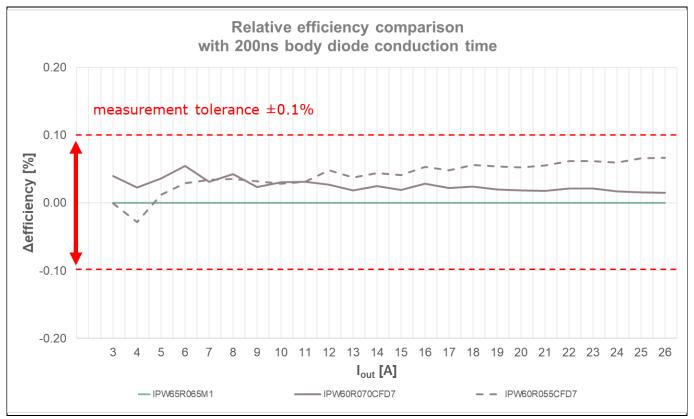

The diode conduction time is very important. The following efficiency comparison shows the impact of CoolSiC<sup>™</sup> forward voltage and an un-optimized dead-time setting. All devices present in this comparison have ZVS. The board has a minimum dead-time of 200 ns, so a full optimization per device is not possible.

#### Benchmarking in target applications

Figure 30 Relative efficiency comparison with 200 ns body diode conduction time

This leads to long diode conduction times, which will in turn lead to lower efficiency. Therefore, customers need to take special care of the dead-time changes and be aware that plug-and-play is generally not recommended in any resonant topology.

## 6 Summary

In summary:

CoolMOS<sup>™</sup>:

- Cost-effective solution for SMPS up to 97 percent system efficiency

- Easy to use

- Most granular portfolio

- Proven quality

$CoolSiC^{TM}$ :

- Cost-effective solution for SMPS greater than or equal to 97 percent system efficiency

- Easy to use, with recommended driving voltage of 18 V turn-on and 0 V turn-off

- Indicated for high-power applications

- Most suitable in any application where hard commutation on a conducting body diode is present or might occur

## **Revision history**

| Document version | Date of release | Description of changes   |

|------------------|-----------------|--------------------------|

|                  |                 | Release of final version |

|                  |                 |                          |

|                  |                 |                          |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-01-16

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document? Email: erratum@infineon.com

č

Document reference AN\_1907\_PL52\_1911\_144109

#### **IMPORTANT NOTICE**

The information contained in this application note is given as a hint for the implementation of the product only and shall in no event be regarded as a description or warranty of a certain functionality, condition or quality of the product. Before implementation of the product, the recipient of this application note must verify any function and other technical information given herein in the real application. Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind (including without limitation warranties of noninfringement of intellectual property rights of any third party) with respect to any and all information given in this application note.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contair dangerous substances. For information on the types in question please contact your nearest Infineor Technologies office.

Except as otherwise explicitly approved by Infineor Technologies in a written document signed by authorized representatives of Infineor Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof car reasonably be expected to result in personal injury.