AIやIoT技術の進化により、膨大なデータを扱う現場では「高信頼メモリ」の重要性が急速に高まっています。AI開発や組込みシステムの分野でも、メモリエラー対策は製品品質を左右する重要なテーマです。

中でも「ハミング符号」は、DRAMやSSDなど多くのメモリ製品で採用されている、実装が容易で高効率な誤り訂正技術として注目されています。特に自動運転や産業機器、医療機器などの分野では、メモリエラーがシステム障害や安全性低下といった致命的なリスクとなるため、高信頼メモリの導入が不可欠です。

本コラムでは、ハミング符号の基本原理から最新の応用事例まで、開発現場で役立つポイントを分かりやすく解説します。

ハミング符号の概要

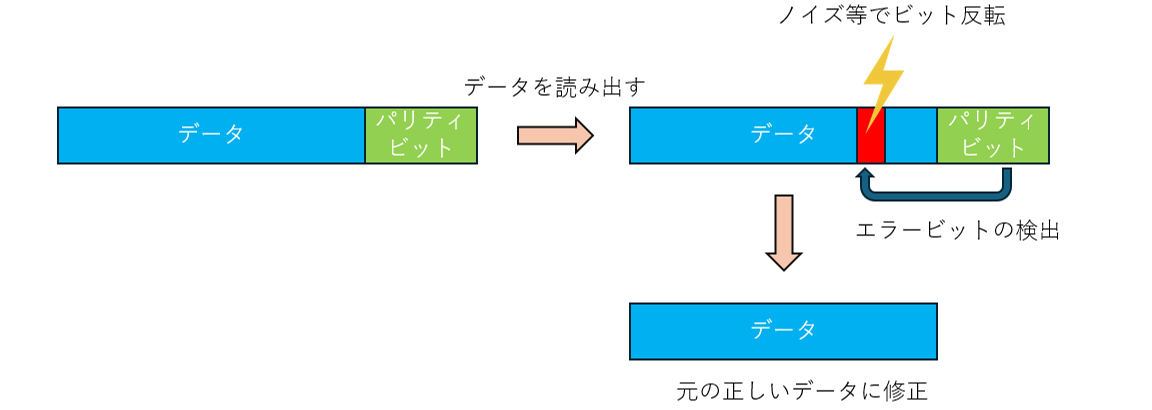

1950年にリチャード・ハミング博士によって発明されたハミング符号は、誤り訂正技術の中でも基礎となる方式です。現在も多くの分野で利用されており、誤り訂正技術の発展に大きく貢献しています。ハミング符号は、元データに追加のパリティビット(誤り検出用の追加情報)を付加することで、1ビットの誤りを自動的に検出し訂正できる技術です。この技術はAIシステムや組込み機器の信頼性向上に大きく寄与しており、システムの安定性および安全性の向上に役立っています。

次項よりハミング符号による誤り訂正の仕組みを詳しく解説していきます。

パリティビットのイメージ

本記事では、現場のエンジニアが実際に導入・運用するケースが多い「ハミング(7,4)符号」と「拡張ハミング符号(SECDED)」に焦点を当てて解説します。ハミング符号は他にも、データ長や用途に応じて、(15,11)符号や(31,26)符号なども存在しますが、組込み分野やメモリ分野では(7,4)と拡張型が主流です。

ハミング(7,4)符号とは

ハミング(7,4)符号は、4ビットのデータに3ビットのパリティビットを追加し、合計7ビットで1ビット誤りの検出・訂正ができる誤り訂正符号です。「7,4」とは7ビット中4ビットがデータ、3ビットが誤り検出・訂正用のパリティビットであることを意味します。計算負荷が少なく、組込み機器やメモリ製品など多くのシステムで広く利用されています。

ハミング(7,4)符号の構成は、以下の通りです。

ハミング(7,4)符号:出力符号語の構成

- 入力データビット(D1~D4):元となる4ビットのデータを指します。

- パリティビット(P1~P3):特定のデータビットの組み合わせをXOR演算で算出し、誤り検出・訂正に利用します。

- 出力符号語(7ビット):データビットとパリティビットを組み合わせて生成される7ビットの送信データです。

誤り訂正の流れ

ハミング(7,4)符号における誤り訂正の流れを解説します。

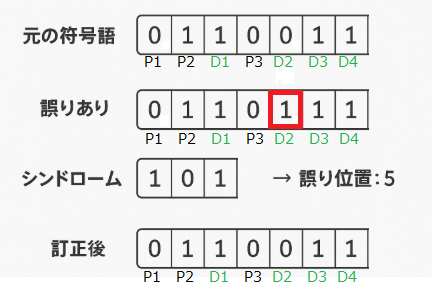

例として、元の7ビット符号語 [0, 1, 1, 0, 0, 1, 1]のデータ伝送時に、ビットD2が反転する1ビット誤りが発生した場合のデータの自動訂正の仕組みを見てみましょう。

ハミング(7,4)符号:誤り訂正の流れ

1.元の符号語は、データビット[1, 0, 1, 1]にパリティビットが付与された、7ビット符号語[0, 1, 1, 0, 0, 1, 1]です。

2.データ送信時に5番目のビットD2が誤って反転し、[0, 1, 1, 0, 1, 1, 1]が受信されました。

3.受信側では、検査行列Hを使ってシンドローム(誤りパターン)[1, 0, 1]を計算し、誤りビット位置を特定します。

4.検出した誤りビットD2を反転することで、元の正しいデータに自動訂正されました。

検査行列Hのイメージ

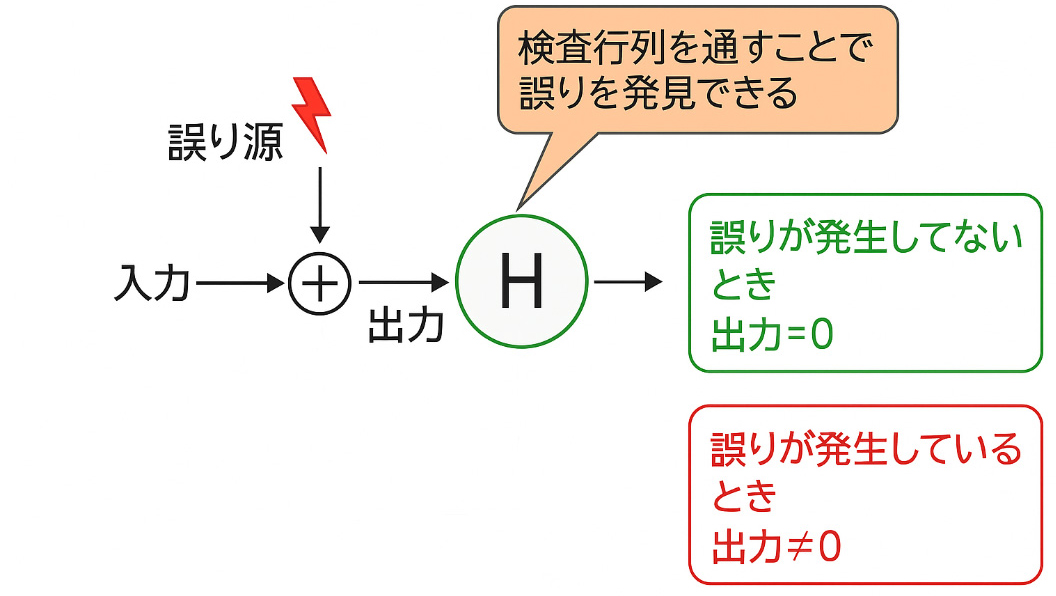

検査行列 Hの役割

ハミング符号における検査行列 H は、パリティビット設計・検証ルールを体系化したもの「設計図」であり、誤り訂正の基盤となります。具体例として、(7,4)ハミング符号の検査行列Hを次に示します。

各列はビットがどのパリティ式に参加するかを示し、列番号の二進表現が対応するパリティ式を表します。

受信ベクトル r(データ+パリティ)に検査行列Hを掛け、mod2演算(※)でシンドローム s を計算します。この値が誤り検出の鍵となります。これを式で表すと次の通りです。

シンドロームsが誤り位置を示す座標となり、単一ビット誤りを一意に特定できます。

※mod2演算:2で割った余りを求める演算で、結果は0または1になります。

直感的には、H は「誤り検出の地図」、シンドロームは「地図上の座標」で、該当列が誤り位置を示します。

拡張ハミング符号とは

拡張ハミング符号は、1ビット誤りの訂正に加えて2ビット誤りの検出(SECDED)も可能な方式であり、サーバーや車載、産業機器、IoT分野など幅広い用途で活用されています。メモリ分野では、拡張ハミング符号は主に「オンダイECC」と「インラインECC」の2つの方式で利用されており、それぞれ用途や特徴が異なります。オンダイECCはメモリコントローラ側で誤り訂正を行うことで、データ伝送経路全体の信頼性を高めます。一方、インラインECCはデータ本体とECCコードを同じメモリ空間に格納することで、システム全体の安全性とエラー検出能力を向上させる方式です。

ここでは、SECDEDとオンダイECC、インラインECCの特徴について解説します。

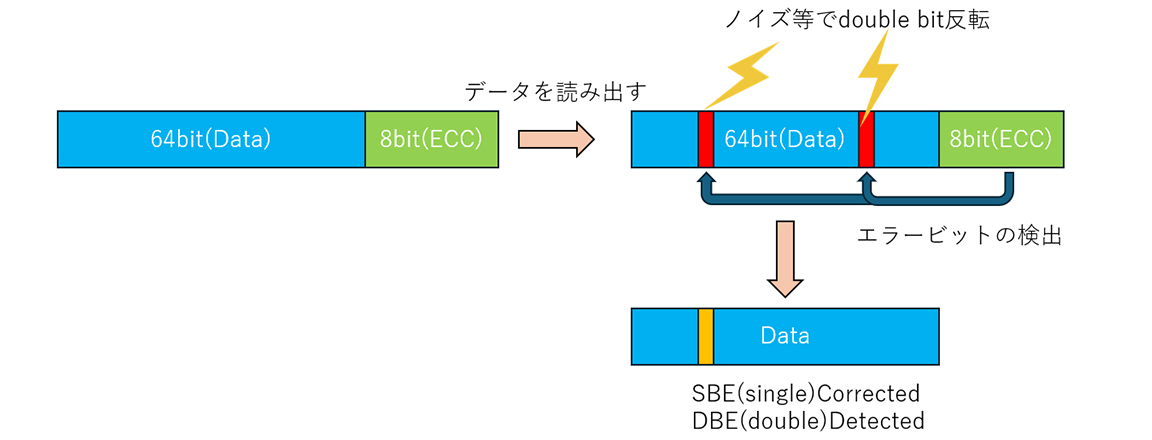

SECDED

SECDED(Single Error Correction, Double Error Detection)は、ハミング符号に追加のパリティビットを加えることで、1ビット誤りの訂正(Single Error Correction)と2ビット誤りの検出(Double Error Detection)を可能にした拡張誤り訂正コードです。現在、DRAMやフラッシュメモリなど多くのメモリ製品で標準的に採用されています。1ビット誤りはパリティチェックにより位置を特定して訂正可能、2ビット誤りはグローバルパリティにより訂正不能エラーとして検出されます。この設計により、訂正可能な範囲を維持しつつ、検出精度を高めています。

メリット

- 単一ビット誤りは訂正、二重ビット誤りは検出できるため、システム障害を未然に防ぐことができます。

- 追加ビット数が少なく、メモリ容量の増加を最小限に抑えられます。

- ハードウェア実装が容易で、DRAMコントローラやSSDコントローラに組み込みやすいのも特徴です。

デメリット

- オーバーヘッドが大きい(例えば、64ビットデータに8ビットのECCを追加する場合、約12.5%の容量増)

- 計算コスト・遅延(誤り訂正・検出のためにエンコードとデコード処理が必要)

- ダブルビット誤りは訂正できない(2ビットの誤りは検出できるが、訂正は不可能)

SECDEDのイメージ

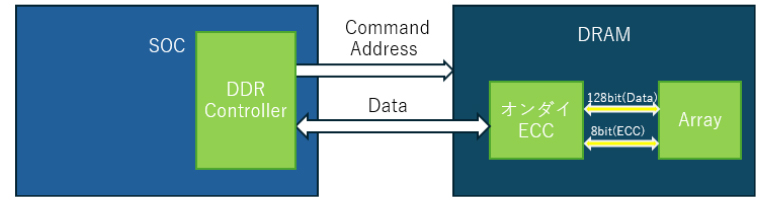

オンダイECC (On-Die ECC)

大容量・高スループットのメモリでは、より大きなデータ単位で効率的に誤り訂正できる方式が必要となるため、ハミング(7,4)符号のような小規模な符号は適していません。この課題を改善ずるため、オンダイECCでは128ビットのデータに8ビットのパリティビットを加えて、合計136ビットの符号語を生成します。これにより、大容量データでも効率的に誤り訂正が可能となり、主にDRAMチップ内部で発生するエラーを訂正する目的で設計されています。

メリット

- DRAMチップ内部でエラー訂正を行うことで、製造時の微細な欠陥による不良品率(歩留まり)を低減できます。

- エラー訂正処理がチップ内部で完結するため、システム全体のレイテンシ(遅延)にほとんど影響しません。

- システム側の設計変更が不要なため、追加コストを抑えてエラー訂正機能を実装できます。

デメリット

- 1ビット誤りの訂正は可能ですが、2ビット以上の誤りは検出できません。

- システム側からはエラー訂正の動作が見えません。そのため、障害発生時の原因解析が難しく、システム全体の信頼性・可用性・保守性(RAS)の向上には限界があります。

オンダイECCのイメージ

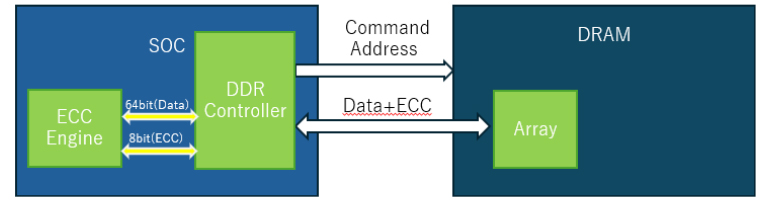

インラインECC (Inline ECC)

インラインECCは、DRAMコントローラがECCコードを生成・検証します。データ本体とECCコードを同じDRAMチップ内に格納することで、データ伝送経路全体の信頼性を高めます。メモリセル内のビットエラーだけでなく、コントローラとDRAM間のデータ伝送時に発生するエラーも検出・訂正することが可能です。反面、データ本体とECCコードを同じメモリ空間に格納するため、ECC用の追加ビット領域が必要となります。

このインラインECCでは、SECDED方式のハミングコードが広く利用されておりシステム全体の信頼性向上に寄与しています。

メリット

- SECDED方式により、1ビット誤りの訂正と2ビット誤りの検出が可能となり、システム全体の信頼性を大幅に向上できます。

- メモリコントローラでエラー管理ができるため、エラーログの取得やRAS機能との連携が容易です。

- 車載や産業機器など、高い信頼性が求められる用途に最適です。

デメリット

- ECCコードの追加により、メモリ容量の約12.5%がオーバーヘッドとして必要となります。

- ECC処理のため、データの読み書き時にわずかな遅延が発生します。

- ECC対応のコントローラとDRAMが必要となるため、実装コストはやや高くなります。

インラインECCのイメージ

以下に SECDED・オンダイECC・インラインECCを比較しました。

SECDED・オンダイECC・インラインECCの比較表

| 項目 | SECDED | オンダイECC | インラインECC |

|---|---|---|---|

| 主な用途 | サーバー・高信頼メモリ(DIMM) | DRAMチップ内部のセル誤り補正 | ストレージや通信での伝送経路を含むデータ保護 |

| 誤り訂正能力 | 1ビット訂正、2ビット検出 | 主にセルレベルの1ビット訂正 | 容量に応じて柔軟(複数ビット訂正可能) |

| 検出能力 | ダブルビット誤り検出 | ダブルビット以上は検出不可 | 実装次第で強力な検出が可能 |

| オーバーヘッド | ECCビット追加(例:64bit+8bit) | チップ内部のみ、外部には影響なし | 実装により大きく変動 |

| 性能影響 | 読み出し時にシンドローム計算で遅延 | 外部I/Fにはほぼ影響なし | 実装によってはレイテンシ増加 |

ハミング符号の応用例

ここでは、ハミング符号の代表的な応用例を、メモリ、ストレージ、通信、車載・産業機器、そしてFPGA・ハードウェアIPの5つの分野に分けて解説します。各分野でどのように誤り訂正技術が組み込まれ、システムの安全性や性能向上に貢献しているのかを具体的な事例とともに見ていきましょう。

1.メモリ分野(ECCメモリ)

AI・IoTの進展により、サーバーやワークステーションではECCメモリが標準的に採用されています。

例えば、(72,64) SECDEDコード(64ビットデータ+8ビットパリティ)はDDR4/DDR5、LPDDR5などのメモリコントローラが実装されており、宇宙線や電圧変動によるソフトエラーからシステムを保護します。

代表的な導入例として、IBM System/360、Intel Xeon、ARMベースSoCなどが挙げられます。

2.ストレージ分野

SSDやRAIDシステムでは、データ保持の長期信頼性向上のためにSECDEDが採用されています。RAID2やエンタープライズSSDで利用されており、低オーバーヘッドで高い誤り検出能力を実現しています。

3.通信システム

衛星通信や無線LAN、IoT通信などノイズや干渉が多い環境でも、拡張ハミング符号を組み込むことで通信効率とセキュリティを強化できます。IoT機器への導入により、通信精度とデバイス性能の向上が確認されています。

4.車載・産業機器

車載SoCや産業用制御システムでは、SECDEDが採用されています。1ビット訂正と2ビット検出が必須要件となっており、LPDDRメモリとインラインECC構成で利用されています。

5.FPGA・ハードウェアIP

FPGA向けIPコアとしては、Vivadoなどで利用可能な72ビット拡張ハミングデコーダ(64ビットデータ+8ビットECC)があり、高信頼通信やデータストレージ向けに最適化されています。シングルビット訂正とダブルビット検出、エラーモニタリング機能を備えています。

まとめ

ハミング符号は、誕生から半世紀以上経った今も、メモリや通信分野の基盤技術として進化を続けています。シンプルな構造と高効率な誤り訂正能力により、DRAM、SSD、ネットワーク機器、組込みシステムなど幅広い領域で採用されています。今後も、高信頼性が求められる分野(自動運転、産業IoT、医療機器、クラウドサーバーなど)において、ECC機能の中核として重要な役割を果たし続けるでしょう。

当社では、用途やご要望に応じた各種メモリ製品をご提案可能です。製品選定や技術的なご相談は、ぜひお気軽にお問い合わせください。

お問い合わせ

関連製品情報

コネクテッドインテリジェントエッジ(Connected Intelligent Edge)を実現する Qualcomm IoT Application Processors

QualcommのIoT Application Processorsは、AIや5Gを活用し、ロボティクスやスマートカメラなどの多様なIoTソリューションを提供します。

- Qualcomm Technologies, Inc.

- NEXT Mobility

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

CodeMeter ソフトファイルによるライセンス制御

ソフトファイルによるライセンス制御ができるCmActLicenseなら、ハードウェア不要で不正コピー・無断使用を強力に防止します。

- WIBU-SYSTEMS AG

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

- ソフトウェア

NXPの車載統合マイコンS12 MagniVの魅力を徹底解説

NXPの統合マイコンS12 MagniVは、ECUの小型化と短期開発を実現し、車載システムの電動化に貢献します。S12 MagniVの特長や利点を解説しています。

- NXP Semiconductors N.V.

- NEXT Mobility

- ICT・インダストリアル

CodeMeterでPythonコード暗号化・難読化&ライセンスビジネスによる収益化

Wibu-SystemsのAxProtector Pythonで、Pythonコードを強力に暗号化し、多様なライセンスモデルで収益化を実現しましょう。

- WIBU-SYSTEMS AG

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

- ソフトウェア

CodeMeterによるソフトウェア保護とライセンス付与

Wibu-SystemsのAxProtectorは、PythonやNvidia Jetsonなど多様なコードに対応し、ソフトウェア全体を強力に暗号化します。

- WIBU-SYSTEMS AG

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

- ソフトウェア

CodeMeter クラウドによるユーザアカウントライセンス制御

クラウドベースのライセンス管理で、ソフトウェアの保護とライセンシングを効率化します。柔軟なライセンス運用と強固なセキュリティを実現します。

- WIBU-SYSTEMS AG

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

- ソフトウェア