EMC設計の基本:失敗しないための3原則

~これからEMC設計を始める方へ~

近年、製品に搭載されるデバイスはますます高周波化・大電流化が進み、EMC設計において考慮すべき要素は年々増加しています。一方で、回路の大規模化や開発スピードの加速により、設計初期段階でEMCまで十分に配慮することが難しくなっているのも事実です。

EMC設計は、明確な方針を持たずにやみくもに取り組むと、対策部品の追加やレイアウト修正を繰り返すことになり、開発期間の長期化やコスト増加につながりやすい分野です。そのため、後工程での対処療法に頼るのではなく、設計の初期フェーズから効率的にEMCを確保する考え方が求められます。

本コラムでは、これから初めてEMC設計に取り組む設計者の方を主な対象として、EMC設計における基本的な考え方について解説します。特別な部品や高度な対策手法を紹介するのではなく、原理試作や初回試作の設計段階から意識しておくべきポイントに焦点を当て、EMCトラブルを未然に防ぐための考え方を整理していきます。

1.はじめに

EMCとは何か

EMC(Electromagnetic Compatibility:電磁両立性)とは、機器やシステムが周囲の電磁環境において意図した機能を安定して発揮する能力、および他の機器へ許容範囲を超える電磁妨害を与えない能力を指します。

EMCは、主に以下の2つの観点から構成されます。

- EMI (Electromagnetic Interference:エミッション)

機器から外部へ放射または伝導される電磁ノイズ - EMS (Electromagnetic Susceptibility:イミュニティ)

外部から加わる電磁妨害に対して、機器が影響を受けずに正常動作を維持できる能力

図1

製品カテゴリとEMC要求レベル

EMCに関する要求レベルは、製品カテゴリや用途、販売地域によって異なり、各種法規制や規格によって定められています。

例えば、民生機器・産業機器・車載機器などでは適用されるEMC規格が異なり、それぞれに応じた設計配慮が必要となりますので、EMC設計では、設計初期段階から対象製品に適用される規格や要求事項を十分に把握したうえで、設計方針を構築することが重要です。

EMC視点で見る設計工程

製品開発におけるEMC設計の重要性は誰もが理解しているところだとは思いますが、実際の設計現場では機能実現や一般性能の確保、コスト、試作スケジュールといった制約が優先され、EMCへの配慮は後回しになりやすいのが実情です。その結果、開発プロセスの後半になって初めてEMC問題が顕在化するケースも少なくありません。

EMC対策には、基板の層構成変更や筐体構造の見直しなど、設計の根本に関わる対応を伴うことがあり、その内容によっては試作ステップの追加が発生し、設計工数・コスト・スケジュールに大きな影響を及ぼします。

そのため、いかに設計初期段階からEMCを意識した設計を行えるかが、製品開発の成否を左右する重要な要素であると言っても過言ではありません。

本コラムでは、設計初期段階で押さえておくべきEMC設計の基本的な考え方について解説します。

2.EMC設計の基本的な考え方

EMC設計とは、評価試験の段階で対策部品を追加して解決することではなく、回路、基板レイアウト、筐体構造等、設計初期の段階から意識的に織り込むべきものです。

一見複雑に見えるEMCの問題も設計の視点で整理すると、実は次の3つの観点に集約して捉えることができます。

① ノイズを発生させない

② 発生したノイズを外部に漏らさない

③ 発生したノイズを減衰させる

この順序には明確な意味があります。

まずノイズの発生そのものを抑え、それでも発生するノイズを外部へ広げない構造とし、最後に残ったノイズを対策部品や回路で弱める、という考え方です。

以降では、この3つの観点について、設計初期に特に意識すべきポイントを解説します。

① ノイズを発生させない (発生源対策)

発生源対策では、ノイズを出す回路や配線そのものを、ノイズが発生しにくい形に設計することが重要です。

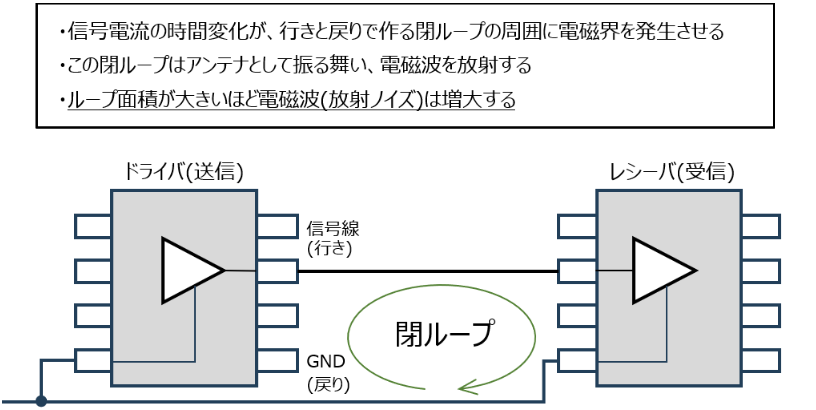

- 電子回路では、電流は必ず「行き」と「戻り」の経路を持っていますので、特に「戻り(リターン)」の経路を明確に意識しながら、回路設計やレイアウト設計を進めることが大切です。

このリターン経路が途中で離れたり途切れたりすると、電流の「行き」と「戻り」で形成される閉ループ面積が大きくなり、電磁ノイズの発生量も増加します。そのため、設計初期段階からループ面積をできるだけ小さく保つ配慮が必要です。

図2

多層基板では信号層の隣接層をGNDプレーン層とすることで、戻り電流が信号直下を最短経路で流れる環境を自然に形成できます。

層構成の制約などから隣接層にGNDプレーンを確保できない場合は、信号線にリターンとなるGND配線を並走させることで、同様の効果を持たせます。

- スイッチング電源など電流変化の大きい回路では特に注意が必要です。

部品配置の段階で、大電流ループが最小の領域で閉じるように配置を検討します。多くのICメーカーは推奨レイアウトパターンを提供しているため、これらを積極的に活用することが効果的です。 - 配線は、急激な線幅変更や不要な枝分かれを避け、素直で連続的な取り回しを心がけます。

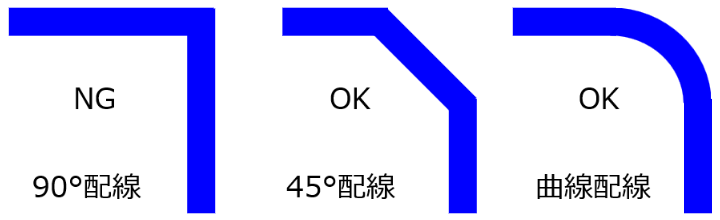

また、直角配線は配線幅を不用意に変動させる要因となるため避け、45度配線や曲線配線など滑らかな取り回しを意識します。

図3

これらは基板構造と配線の基本原則を意識するだけで効果が得られる設計上の重要な考え方となりますので、初回試作の段階でこれらを確実に押さえておくことで、後工程での追加対策工数の大幅な削減が期待できます。

② 発生したノイズを外部に漏らさない (封じ込め対策)

筐体の隙間、ケーブル、I/Oコネクタは、ノイズが外部に漏れやすい場所ですので、これらの部位からノイズが広がらないように、構造的に封じ込める設計が重要となります。

- 金属筐体は、合わせ目や固定部含めて隙間を作らず、ノイズの漏洩を抑制します。

- ケーブルのシールドは、一般的に筐体のシャーシGNDに接続して、ノイズ放射を抑える設計が推奨されます。

- I/Oコネクタ周辺では、内部の各配線に乗ったノイズが外部に広がらないよう、コンデンサ等でGNDへ逃がす経路を確保します。

これらの封じ込め対策は、開発の後段での修正が特に難しく、対応内容によっては工数とコストが大きく増加します。したがって、設計初期の段階から十分に検討し、構造とレイアウトへ確実に反映することが、開発全体の工数・コスト削減につながります。

③ 発生したノイズを減衰させる(減衰対策)

発生源対策や封じ込め対策だけでは、機器が要求仕様として定めるノイズレベルを満たせない場合があります。

その際に適用するのが、残留ノイズを低減する減衰対策です。

- 電源ライン:電源入力部にLCフィルタなどを配置し、内部で発生したノイズを効果的に減衰させます。

- 信号ライン:差動信号ではコモンモードチョークによりコモンモードノイズを抑制します。シングルエンド信号では、ダンピング抵抗・フェライトビーズ・対GNDコンデンサなどを組み合わせ、信号品質を確認しながら最適な構成を検討します。

ただし、減衰対策のみでノイズを規格レベルまで抑えることは難しいケースが多いため、基本方針としては

①発生源対策 → ②封じ込め対策 → ③減衰対策

の順で対策を構築し、減衰対策はあくまで補助的な役割として位置付けるのが適切です。

3.まとめ

EMC設計は、開発後段にて対策部品を追加するだけで十分な効果を得ることは難しく、場合によっては設計の大幅な手戻りを招く原因となります。

そのため製品設計においては、設計初期段階からEMC対策の基本原理を十分に意識して進めることが重要です。

具体的には、

①発生源対策でノイズの発生自体を抑え、

②封じ込め対策で外部への漏れを防ぎ、

③減衰対策で残ったノイズを抑える、

という順序で設計に組み込むことが有効です。

この順序を意識することで、「問題が発覚してから慌ててEMC対策を後付けで行う」といった対処的アプローチではなく、設計初期段階からEMC対策を計画的に織り込むことができ、後工程での修正や追加対策を最小限に抑えることができます。

本稿で紹介した考え方が、効率的かつ確実なEMC設計を進めるうえでの一助となれば幸いです。

また当社では、お客様の要求EMC性能や製品特性に応じた各種対策製品のご提案、ノイズ対策に関する技術支援に加え、ODM/EMSパートナーと連携した製品開発立ち上げ支援のスキームも提供しております。

これらの内容に関して、お困りの点などございましたら、お気軽にお問い合わせください。

お問い合わせ

関連製品情報

新LTspice③パラメトリック解析、公差解析

LTspiceはアナログ・デバイセズ提供の無償SPICEシミュレーターです。パラメトリック解析や公差解析の手法、ドットコマンドの使い方を紹介します。

- Analog Devices, Inc.

- NEXT Mobility

新 LTspice②SPICEモデル使用方法

LTspiceは、アナログ・デバイセズが無償で提供するSPICEシミュレータです。デモ回路の入手方法や各モデルを紹介します。

- Analog Devices, Inc.

- NEXT Mobility

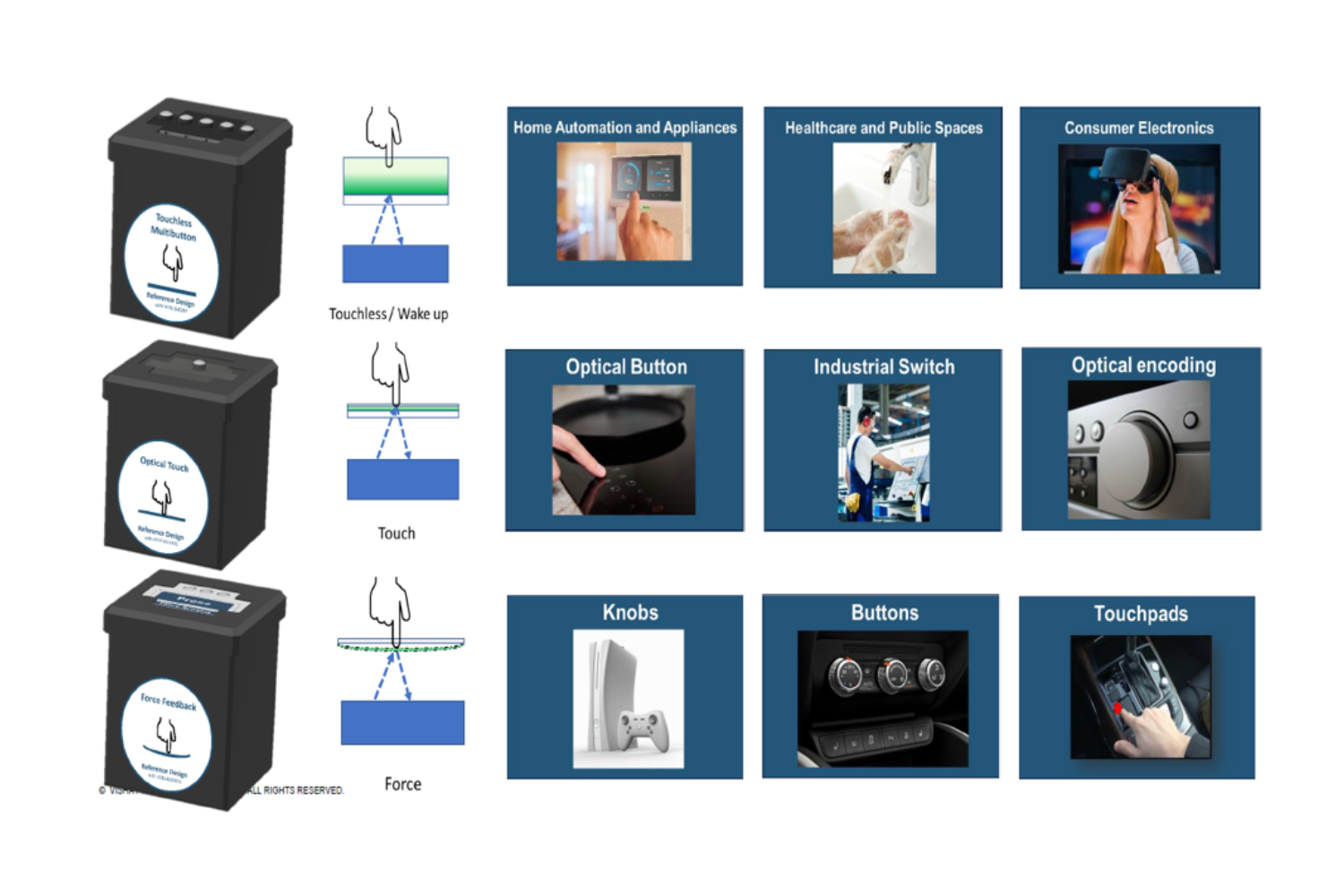

光センサーReference Design:光学式センシングで進化する次世代 HMI — Touchless / Optical Touch / Force Sensing の3方式を徹底解説—

Vishayの光学式センシングHMI向けReference Designを紹介し、非接触・光学タッチ・フォース検知の設計要点を解説します。

- Vishay Intertechnology, Inc.

- NEXT Mobility

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

新LTspice完全ガイド①

LTspiceとは、アナログ・デバイセズが無償で提供するSPICEシミュレータです。バージョンアップしたLTspice24の変更点や性能を解説します。

- Analog Devices, Inc.

- NEXT Mobility