■ はじめに

近年の車載ECUでは、複数カメラの映像処理やAI推論が一般的になっており、SoCが扱うデータ量は急速に増加しています。一方で、ECUは車載電源の厳しい制約下において、−40℃〜125℃という広い温度範囲への対応も必要です。車載電源は大きな電圧変動にさらされる環境であるうえ、車両全体で使用可能な電力にも限りがあります。こうした条件の中でECUは、限られた電力と不安定な電源環境に耐えながら、安定した動作を維持しなければなりません。そのため、車載ECUの開発においては、消費電力および発熱の管理が重要な設計課題となっています。

特に、SoC と大量のデータをやり取りするメモリーは電力と発熱に大きく影響するため、処理性能を引き上げるうえでもその重要性はこれまで以上に増していきます。スマートフォン向けに発展してきた

LPDDR 系のメモリーは、低消費電力と高いデータレートを両立できる特性から、車載ECUでも採用が拡大しています。本稿では、メモリーの基礎から DRAM の性質、そして LPDDR4 と

LPDDR5 の違いまでを、初めての方でも理解しやすいよう順を追って解説します。

1. メモリーとは

メモリーは揮発性と不揮発性に大別されます。揮発性は電源断で内容が消失し、不揮発性は電源断後もデータを保持します。

揮発性メモリーは読み書きが高速で、プロセッサーがリアルタイムで扱うデータを保持する領域として使われます。一方、不揮発性メモリーはソフトウェアの保存や初期化情報の格納といった用途に使われ、メモリーの役割は用途に応じて明確に分かれています。

2. DRAMとは

DRAM(Dynamic RAM)は揮発性メモリーの代表で、構造が比較的単純で大容量化しやすく、PC・スマートフォン・車載を含む多くの機器で作業領域として使われています。車載向け SoC では、画像処理や

AI 推論など、データを広帯域でやり取りする処理が増えており、DRAM の性能がそのままシステム全体の性能に影響を与えます。

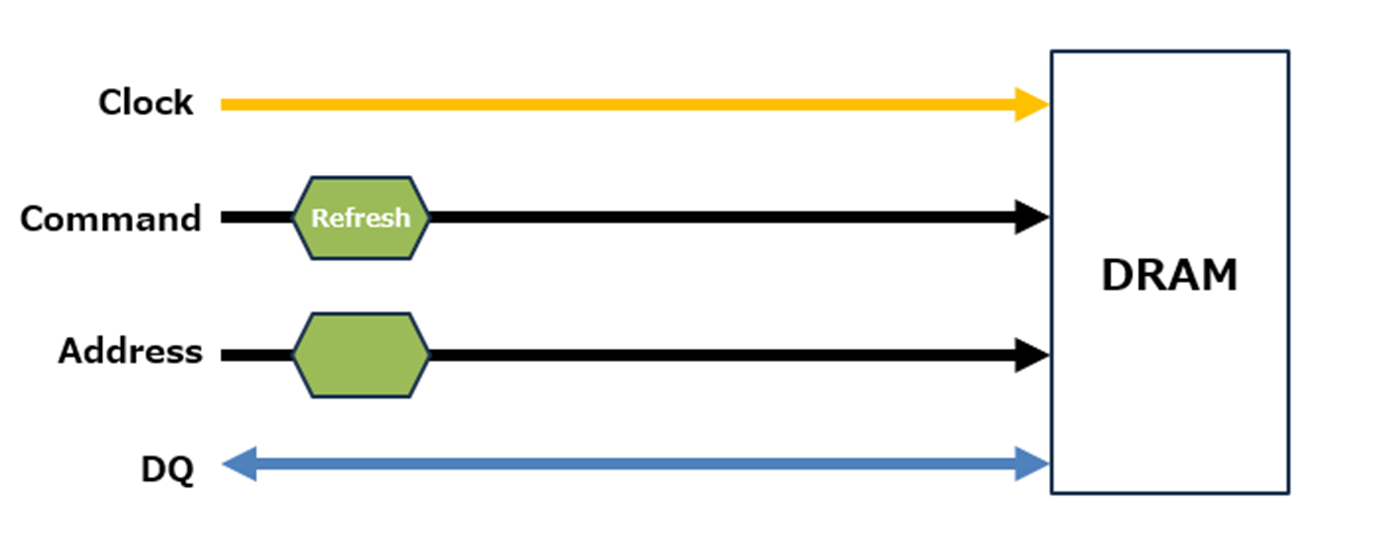

DRAMは、電荷を蓄える小さなコンデンサを利用してデータを保持する仕組みを持っています。しかし、この電荷は時間とともに自然に減っていくため、定期的にリフレッシュと呼ばれるデータの再書き込みが必要です。

温度が上がると電荷が失われるスピードも速くなるため、リフレッシュをより短い間隔で行わなければなりません。このリフレッシュ動作は、メモリーが本来の読み書きに使える時間を圧迫するためレイテンシに影響し、また、リフレッシュ回数の増加は内部回路の動作回数を増やすため消費電力の増加にもつながります。そのため、車載のように高温での動作が前提になる用途では、DRAMは温度上昇によるパフォーマンスの影響を受けやすいという特徴があります。

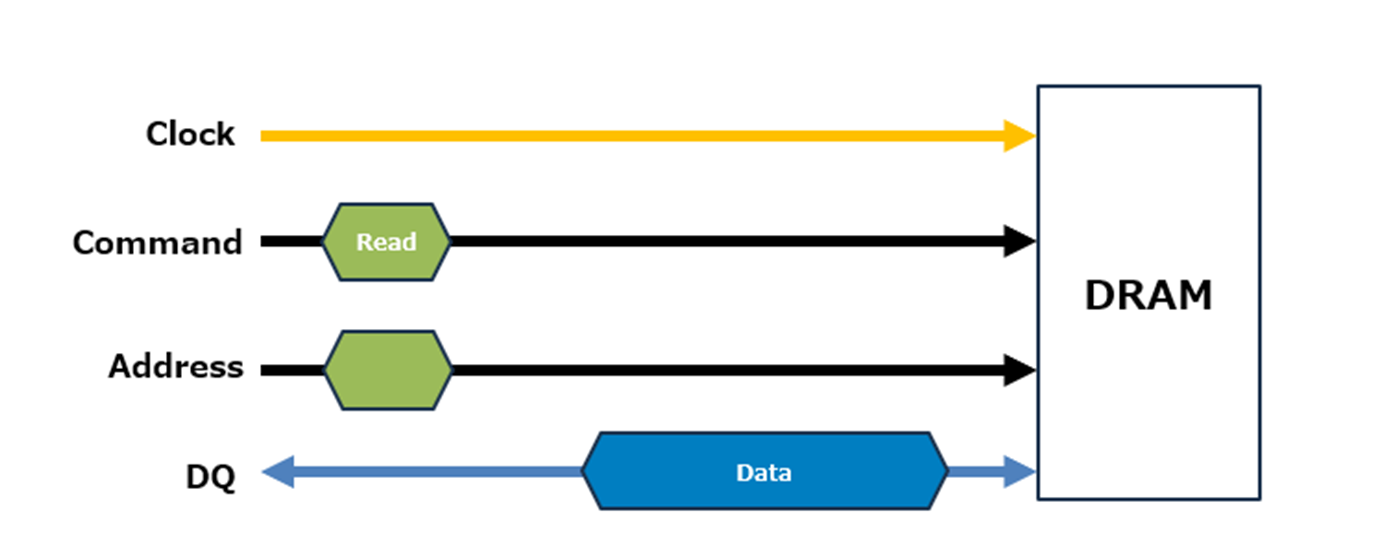

DRAM は、コントローラーが CA(Command / Address) と呼ばれる信号線を介して、読み出し(Read)、書き込み(Write)、リフレッシュ(Refresh)

といった各種操作を指示することで動作します。CA 信号は、DRAM に対して「どの操作を」「どのアドレス(バンク、行、列)に対して」実行するかを伝える役割を担います。

これらのCommandやAddressは、DRAM に入力される CK(Clock)信号に同期します。DRAM は基本的に同期型メモリーであり、CK の立ち上がり(または立ち下がり)エッジを基準として

CA 信号をサンプリングすることで、内部動作のタイミングを決定します。

一方、実際にデータの読み書きを行う際には、DQ(Data)信号と呼ばれるデータバスが用いられます。Write 動作では、コントローラーが DQ 信号に書き込みデータを出力し、DRAM

がこれを受信します。Read 動作では、DRAM が DQ 信号を駆動してデータを出力し、コントローラーがこれを受信します。このとき、DQ

信号の有効なサンプリングタイミングはクロックに対して厳密に規定されています。

このように、CA 信号が「何をするか」を指定し、クロックが「いつそれを行うか」を決め、DQ 信号が「実際のデータ」を転送するという役割分担によって、DRAM

の基本動作が構成されています。

この CA・CK・DQ という関係を理解しておくことは、後に登場する LPDDR5 における WCK(Write Clock)や RDQS(Read Data

Strobe)といった信号を理解する上でも重要であり、DRAM 動作原理を学ぶための基礎となります。

Readコマンドとデータの関係

Refreshコマンド

DRAM には LPDDR のほかにも、PC 向けの DDR、GPU 向けの GDDR、3D 積層で高帯域を実現する HBM などさまざまな種類があります。これらの中で、車載用途では性能と消費電力のバランスに優れる LPDDR 系が有力候補であり、その世代ごとの進化は車載システムの性能向上に直結します。以下に主な DRAM の種類を整理します。

| 種類 | 特徴 | 用途 |

|---|---|---|

| SDRAM | クロック同期型。CPUと同期して動作するため高速。 | 古いPCや組み込み機器 |

| DDR SDRAM | クロックの立ち上がりと立ち下がりの両方でデータ転送。 | 一般的なPCやノートPC |

| LPDDR | 低消費電力版DDR。モバイル向け。 | スマートフォン、タブレット |

| GDDR | GPU向けに最適化された高速メモリー。 | グラフィックカード |

| HBM | 高速・高帯域・省スペース。3D積層構造。 | ハイエンドGPUやAI処理向け |

3. LPDDRとは

LPDDR(Low-Power DDR)は、その名のとおり低消費電力を重視して設計されたDRAMで、スマートフォンの普及とともに進化してきました。低電圧で動く I/O

回路や、細かく電力を制御できるスリープモードを備えているため、一般的な DDR と比べて電力あたりの性能が高く、同じ処理でも発熱を抑えられる点が特徴です。

LPDDR は世代ごとにデータ転送速度(データレート)が大きく向上してきました。データレートを表すMb/s(Megabit per

second)は、1秒間に何回データを転送できるかを示す数字です。LPDDR4

では最大4266Mb/s、LPDDR5では6400Mb/s、LPDDR5Xでは8533Mb/sと、世代が上がるごとに高速化しています。この高速化により、高解像度カメラや高度なAI推論など、大量データを扱うデータにも対応できるようになりました。

| 発表年 | 名称 | JEDEC規格 | データレート |

|---|---|---|---|

| 2006 | LPDDR | JESD209 | ~533 Mb/s |

| 2009 | LPDDR2 | JESD209-2 | ~1066 Mb/s |

| 2012 | LPDDR3 | JESD209-3 | ~2133 Mb/s |

| 2014 | LPDDR4 | JESD209-4 | ~4266 Mb/s |

| 2017 | LPDDR4X | JESD209-4改訂 | ~4266 Mb/s |

| 2019 | LPDDR5 | JESD209-5 | ~6400 Mb/s |

| 2021 | LPDDR5X | JESD209-5改訂 | ~8533 Mb/s |

| 参考 | LPDDR6 | JESD209-6 | 10667 Mb/s~ |

4. LPDDR4 から LPDDR5 への進化

LPDDR5 の特徴を一言でまとめると、「より高速に、より少ない電力で動作するよう全体構造が見直されたメモリー」です。例えば、コマンドを送る CA バスが LPDDR4 の SDR

*1方式から DDR*2

方式に変更されたことで、同じ時間内に転送できる指示の量が増え、高転送レート時のコマンド待ち時間が短縮されました。その結果、実効効率が向上し、高速動作時のオーバーヘッドを低減できます。

こうした高速化を支える鍵となるのが、データ転送時のタイミングを正確に合わせる仕組みです。

従来の LPDDR4 では DQS*3 が読み書き共通で使われていましたが、LPDDR5 では書き込みに WCK*3、読み出に RDQS*3

を用いるように役割が分離されました。送信側と受信側の動作が明確に切り分けられたことで、配線遅延やジッタの影響を受けにくくなり、高データレートでも安定したタイミング同期が可能になります。特に高速領域では微小なスキューが致命的となるため、この構造刷新は信号整合性と安定動作の両立において重要なポイントです。

*1 SDR(Single Data Rate):基準信号の立ち上がり1回につき1回データを転送する方式

*2 DDR(Double Data

Rate):基準信号の立ち上がりと立ち下がりの両方でデータを転送する方式

*3 DQS/WCK/RDQS:DQ転送用信号(データストローブ信号)

LPDDR4のDQS同期

LPDDR5のWCK/RDQS分離

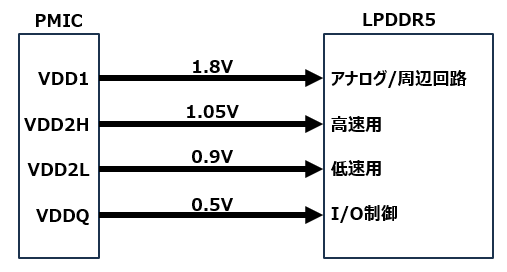

さらに LPDDR5 では電源構造も整理され、VDD1/VDD2H/VDD2L/VDDQ といった電源が用途別に分割されました。

-

VDD1:約1.8V。基準電圧生成や制御ロジックなど、DRAM内部のアナログ・周辺回路を動かすための電源です。

-

VDD2H:約1.05V。高速動作時に使われるコア電源で、高いデータレートが必要な場合に使用されます。

-

VDD2L:約0.9V。低速・省電力動作時のコア電源で、動作周波数に応じて内部回路が自動的に切り替わり、消費電力を抑えます。

-

VDDQ:約0.5V。データの入出力用電源で、非常に低い電圧で動作するため、I/Oの電力を大きく削減できます。LPDDR4からLPDDR5で1.1Vから0.50Vまで下がり、データ入出力に必要な電力が大幅に低減されています。特に車載向けのように熱設計が厳しく、消費電力に明確な上限がある環境では、この差が大きな意味を持ちます。

LPDDR5 電源分離

代表的なLPDDR4とLPDDR5の主な相違点を整理しました。

| LPDDR4 | LPDDR5 | |

|---|---|---|

| パッケージ | 200 ball | 315 ball / 441 ball |

| バス幅 | x32 | x32 / x64 |

| 電圧 |

VDD1 = 1.8V VDD2 = 1.1V VDDQ = 1.1V |

VDD1 = 1.8V VDD2H = 1.05V VDD2L = 0.9V / 1.05V VDDQ = 0.50V / 0.45V / 0.35V |

| クロック周波数 | ~2133MHz | ~800MHz |

| CAバス | SDR : ~2133Mb/s | DDR : ~1600Mb/s |

| データストローブ | DQS : ~2133MHz |

WCK(Write用) : ~3200MHz RDQS(Read用) : ~3200MHz |

| データレート | ~4266Mb/s | ~6400Mb/s |

5. データ入力スペック(Mask方式)の理解

LPDDR では、メモリーが受信した信号を「正しいデータ」として認識できる範囲を、「どのタイミングで、どの電圧なら読み取れるか」

という形で定義しています。これがデータ入力の許容範囲(入力マージン)です。

従来の方式では、データを読み取るためのセットアップ時間(tDS)とホールド時間(tDH)といった、時間方向だけの基準で評価していました。しかし LPDDR4

から、より正しく波形を評価するために、時間と電圧の両方をまとめてチェックする「Mask方式」が導入されました。これにより、電圧レベルの揺らぎやノイズの影響も含めた、より実効的な安定性評価が可能になっています。

Mask方式は、データの読み取りが安定する範囲を “時間 × 電圧” の四角い枠として定義する方法です。イメージとしては、オシロスコープなどで見る アイパターン(Eye Pattern)

があります。アイパターンは、波形が重なり合って“目”のような形に見える図ですが、この「目(アイ)」が大きいほどデータが読み取りやすく、小さいほど誤りが出やすくなります。Mask方式は、この Mask

の枠に波形(DQ)が収まっていれば OKという考え方で、アイパターンの目の大きさと同じ考え方です。

LPDDR5

ではデータレートがさらに向上したことで、入力マージンとなる許容“窓”が一段と狭くなりました。つまり、タイミングのずれや電圧のわずかな変動でもエラーにつながりやすいということです。そのため、Mask方式を理解しておくことは、配線長のばらつき、電源ノイズ、波形品質といった高速信号を安定させる設計全般において重要な指標となります。

| デバイス | スペック | 例 |

|---|---|---|

| DDR3 | DQ:データ、 DQS:データを読むタイミング |

データレート:2133 Mb/s ① tDS : 55 ps ② tDH : 60 ps |

| LPDDR4 |

データレート:4266 Mb/s ① tDIVW : 58.5 ps ② vDIVW : 120 mv | |

| LPDDR5 |

データレート:6400 Mb/s ① tDIVW1 : 54.6 ps ② tDIVW2 : 28.1 ps ③ vDIVW : 100 mv |

6. 車載・エッジAIへの応用

車載ECUでは、フロントカメラや周囲監視用カメラなど複数の映像を扱い、さらにAIによる物体認識や走行判断などを行う場面が増えています。このような処理は大量のデータを高速にやり取りする必要があるため、LPDDRの持つ高いデータレートは大きな利点になります。

また、車載向けでは長期供給や温度グレードの対応など特有の要件がありますが、近年はLPDDRの車載グレード製品も増え、安心して選べる環境が整ってきました。

エッジAIでも推論の電力効率が重視され、LPDDRの低消費電力特性が適合します。

SoC+LPDDR構成により、オンデバイスAI推論や高解像度映像処理で性能と省電力を両立。

センサーデータのリアルタイム処理には、帯域・レイテンシ・温度特性に優れるメモリーが不可欠。LPDDRは低消費電力と耐環境性の面で採用が進む。

学習(トレーニング)用途ではHBMやGDDRが主力だが、推論や省電力重視のエッジ側ではLPDDRが効果を発揮。発熱・消費電力の制約下で帯域を確保できる点がメリット。

7. まとめ

LPDDR は、低消費電力でありながら高い性能を発揮できるメモリーであり、車載 ECU のような温度条件や電力制約が厳しい環境でも適した選択肢です。なかでも LPDDR4 から LPDDR5

への世代進化では、データレート、コマンド転送方式、タイミング同期の仕組み、電源構造など、複数の要素が大きく改善されています。これらの改良はすべて、高速化と安定性、そして電力効率の向上を目的としたものです。

車載 ECU の設計では、性能だけでなく、高温環境への対応、長期供給、基板レイアウト、電源の品質など、考慮すべき条件が多岐にわたります。LPDDR5

の特性を理解することは、こうした制約下でシステム全体を最適化する上で非常に重要であり、将来の高解像度処理や AI 推論の需要増にも柔軟に対応できる設計につながります。

お問い合わせ

関連製品情報

NOR Flash

NOR Flashは高速読み取りと高信頼性を特徴とし、車載や産業用途など幅広い分野で使用される不揮発性メモリーです。

- Micron Technology, Inc.

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

eMMC

Micron社のeMMCは、高速データ処理と省電力設計を実現し、産業機器やロボティクスでの利用に最適なストレージソリューションです。

- Micron Technology, Inc.

- NEXT Mobility

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

F-RAM(強誘電体RAM) 超高速・高耐久・低消費電力の不揮発メモリー インフィニオンF-RAMでIoTと車載の信頼性を革新

インフィニオンのF-RAMは高速アクセスと不揮発性を両立し、耐久性と低消費電力で車載や産業機器の信頼性向上に貢献します。

- Infineon Technologies AG

- NEXT Mobility

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

CodeMeter クラウドによるユーザアカウントライセンス制御

クラウドベースのライセンス管理で、ソフトウェアの保護とライセンシングを効率化します。柔軟なライセンス運用と強固なセキュリティを実現します。

- WIBU-SYSTEMS AG

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

- ソフトウェア

CodeMeterでPythonコード暗号化・難読化&ライセンスビジネスによる収益化

Wibu-SystemsのAxProtector Pythonで、Pythonコードを強力に暗号化し、多様なライセンスモデルで収益化を実現しましょう。

- WIBU-SYSTEMS AG

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

- ソフトウェア

CodeMeter ソフトファイルによるライセンス制御

ソフトファイルによるライセンス制御ができるCmActLicenseなら、ハードウェア不要で不正コピー・無断使用を強力に防止します。

- WIBU-SYSTEMS AG

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

- ソフトウェア