FETはスイッチング回路や電源設計に欠かせない半導体素子ですが、選定を誤ると効率低下や信頼性問題を招きます。特にオン抵抗や帰還容量、ゲートしきい値などの特性は、損失や発熱に直結します。そこで本記事では、FET選定時に重視すべき5つの性能指標と、設計で押さえるべき堅牢性・コストのポイントを実務目線で整理しました。初期設計の安全側見積もりや、トレードオフの考え方も含め、効率と信頼性を両立するための基本を解説します。

FET選定時に重視すべき5つの性能指標

FETの性能を左右する特性は、主に以下の5つです。

- Rds(on):オン抵抗

- CRSS/CGD:帰還容量・ゲート-ドレイン容量

- Vgs(th):ゲート電圧しきい値

- Qg:ゲート電荷

- 寄生ダイオード

これらについて順に解説します。

FIGURE 1.FET

Rds(on):オン抵抗

FETオン時のドレイン-ソース間に発生する端子間抵抗です。この値はFETのダイ温度に比例する傾向があり、Vgs電圧にも大きく依存します。従って[Figure 2.Rds(on)と条件]のように、データシートでRds(on)が規定されている条件を必ず確認することが重要です。なお下式で、Rds(on)に大きく影響を受ける導通損失を計算できます。

導通損失[W]=オン抵抗[Ω]x実行値電流[A]xオン時間[s]/秒

| SPECIFICATIONS (TJ = 25 °C, unless otherwise noted) | ||||||

|---|---|---|---|---|---|---|

| PARAMETER | SYMBOL | TEST CONDITIONS | MIN. | TYP. | MAX. | UNIT |

| Static | ||||||

| Drain-source on-state resistance a | RDS(on) | VGS = -10 V, ID = -15 A | - | 0.0079 | 0.0096 | Ω |

| VGS = -4.5 V, ID = -15 A | - | 0.010 | 0.0122 | |||

FIGURE 2.RDS(ON)と条件

CRSS/CGD:帰還容量・ゲート-ドレイン端子間容量

CRSSはミラー効果を引き起こす容量、CGDは物理的な端子間容量を指します。両者の定義は概ね同じ容量を意味し、値が小さいほどインバータやスイッチング電源で発生する矩形波の立ち上がり・立下りが急峻になり、スイッチングノイズが増加します。初期設計時には以下の式で遷移損失を安全側に見積もることを推奨します(式のように遷移損失とCRSSは比例します)。

遷移損失[W]=2x最大電圧[V]2x最大電流[A]xCRSS[F]xスイッチング周波数[Hz]

なおスイッチング用途で無ければ、CRSSを重視する必要はありません。またCRSSの小ささと、後述するSOA(安全動作領域)耐量はトレードオフの関係です。

VGS(th):ゲート電圧しきい値

FETの内部にはFETセルが大量に並んでおり、これらが全てオンすることでRds(on)が形成されます。

オンするVgs(th)にはセル間誤差があり、Vgs(th)は全セルのうち一つ以上がONする最小電圧をさします。Vgs(th)付近で動作させると、一部のセルに電流が集中し破壊のリスクがありますので十分なマージンを持った設計が必要です。

Qg:ゲート電荷

FETをオンするのに必要なゲート端子へ供給する必要がある電荷量です。スイッチング回路では、FETをオンするたびにこの電荷量が必要となり、ゲートへの平均入力電流は下式で求めることができます。

ゲートへの平均入力電流[A] = ゲート電荷[C] x スイッチング周波数[Hz]

寄生ダイオード

FETにはソースからドレインへの寄生ダイオードが形成されます。

スイッチング用途では、逆起電力対策としてここにダイオードが必要ですが、寄生ダイオードは特性が悪いため、瞬間的な電圧降下や損失が発生します。必要に応じて高速ダイオードを外付けする事で対策可能です。なお、このダイオードの重要な特性値は、

順方向電圧VF[V]、逆回復時間trr[s]、立ち上げ/下げ時間ton/off[s]です。

FETの堅牢性を高めるための設計ポイント

堅牢性とは、FETが動作中に破壊されず、信頼性を維持できることをさします。そのためには、絶対最大定格や耐量を超えない設計が不可欠です。このなかで特に重要な項目を4つ説明します。

Vds:ドレイン-ソース間電圧定格

Vds値を超えるとFETはブレイクダウンを起こしアバランシェ領域に入ります。理論上はアバランシェエネルギー耐量以下で使えば破壊しませんが、この耐量はわずかなため定格電圧以下で使うことが推奨されます。特にスイッチング回路では、想定外の高電圧が瞬間的に発生することがあるので、適切な波形観測による確認が必要です。

Pd:許容損失

FETが常時消費できる電力損失です。この値は周囲温度や基板条件などにより変動しますので、データシートの記載値を参考にシミュレーションなや熱抵抗の計算を行い、FETが損失に耐えられるかを検討することが重要です。なお損失Pdは、前述の遷移損失と導通損失の合計となります。

Tj:ジャンクション温度定格

パッケージ内部の半導体(ダイ)の最大許容温度です。Tjは直接測定できないため、ケース温度と熱抵抗(RthJC)等を用いて逆算します。

SOA:安全動作領域

FETのパルス耐量を示す指標で下図左のようなイメージで表されます。これの各limitラインを超えるとFETが破壊される可能性があるため、当該ラインを下回ることが必要です。特に二次降伏リミットライン付近では十分なマージン確保が必要になります。なお、SOAカーブの電力リミットラインはディレーティングカーブを参考に調整することが可能です。例えば下図右のように、25℃で200W、75℃で100W損失可能であれば、75℃時のSOA各リミットラインの電流値は、25℃時の半分(100W/200W)となります。

FIGURE3.SOAカーブとディレーティングカーブイメージ

まとめ

FET選定では、オン抵抗やCRSSなどの容量特性が効率を左右しますし、しきい値電圧やSOA対応は信頼性確保に不可欠になっています。そして性能・堅牢性・コストは相互にトレードオフの関係にあるため、用途に応じた設計が重要です。初期段階では最大電圧・最大電流を用いた安全側の損失見積もりを行い、詳細設計ではシミュレーションや実測で補正することを推奨します。弊社では最適なFET選定と技術サポートを提供していますので、ぜひ当社製品ページをご覧ください。

お問い合わせ

関連製品情報

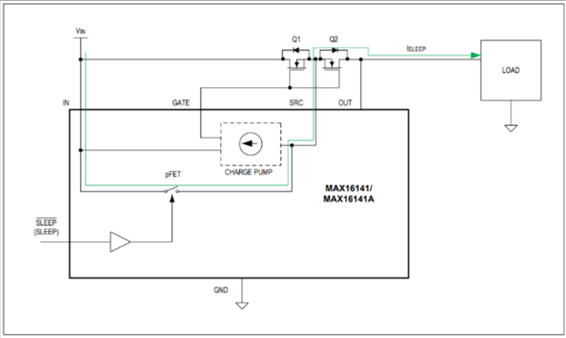

車載バッテリーの逆説保護で用いられるダイオードの損失課題解決

理想ダイオードコントローラーMAX16171/MAX16141で、MOSFETのON/OFFを切り替えて電流の逆流を防ぎ、発熱やシステム効率の改善に繋がります。

- Analog Devices, Inc.

- NEXT Mobility

- ICT・インダストリアル

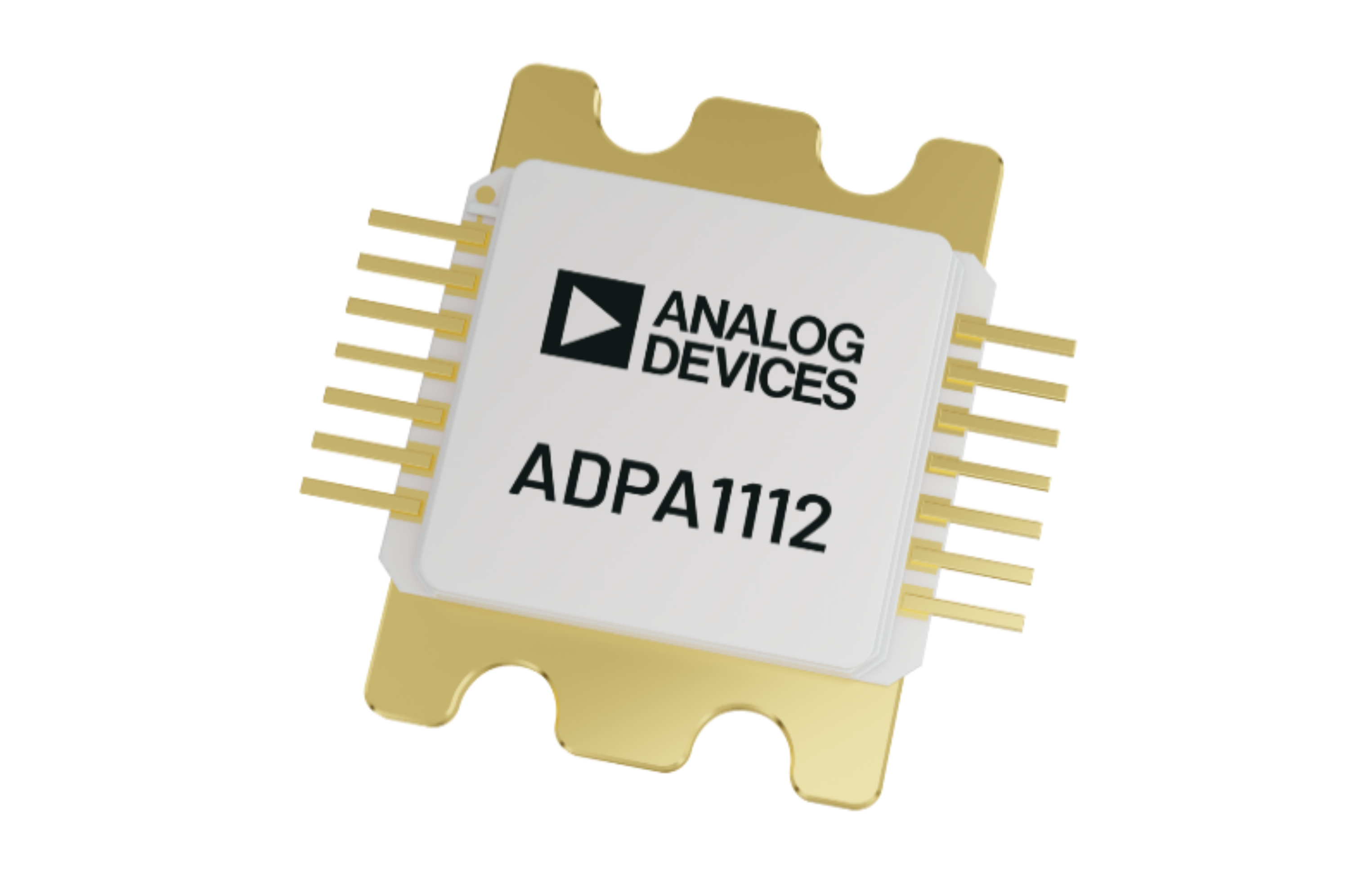

ADPA1112:1GHz~22GHz、15W、窒化ガリウム(GaN)パワー・アンプ

ADPA1112は1GHz~22GHz帯で動作するGaN高出力RFパワーアンプで、電子戦や計測向けに高出力・高効率と評価用ボードやモデルを提供します。

- Analog Devices, Inc.

- ICT・インダストリアル

NXPのNPUを搭載したi.MX/MCXによるエッジAIソリューションをご紹介

利用が急増しているエッジAIについて、実際の機器を踏まえて解説します。NXPがリリースしている、NPUを搭載したプロセッサー、マイコンをご紹介します。

- NXP Semiconductors N.V.

- NEXT Mobility

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

CoolMOS™ 高効率・高信頼のスーパージャンクションMOSFETで電源の省エネと小型化を両立

CoolMOS™ 7/8シリーズは高耐圧・低損失設計で高効率電源を実現し、サーバーや通信、太陽光、EV充電器など幅広い用途に対応します。

- Infineon Technologies AG

- NEXT Mobility

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

車載用MOSFET(20V〜800V) 効率・高信頼性を実現する、次世代車載用MOSFET

インフィニオンの車載用MOSFETは低オン抵抗と高スイッチング性能を持ち、車載電動化に最適な高信頼パワー半導体です。

- Infineon Technologies AG

- NEXT Mobility

- ICT・インダストリアル

NXPの車載CAN/LINトランシーバー製品の特徴を徹底解説

車載ネットワーク製品をお探しのECU開発メーカー様向けに、車載環境の厳しい条件に耐えることのできる、NXPの車載CAN/LINトランシーバー製品の特徴について解説します。

- NXP Semiconductors N.V.

- NEXT Mobility

- ICT・インダストリアル