現代のコンピューターやサーバー、ストレージシステムにおいて、データ転送の高速化は性能向上の鍵を握っています。その中核を担う技術の一つが「PCI Express(PCIe)」です。この記事は初心者エンジニア向けに、PCIeのしくみ/PCIとの違い/階層構造を図表でやさしく解説します。

PCIeとは?電子デバイスの高速道路

PCIe(Peripheral Component Interconnect

Express)は、CPU、GPU、SSD、NICなどの周辺機器を接続するための高速インターフェイス規格です。膨大なデータを効率よくやり取りするには、高速かつ低遅延な通信路が必要です。PCIeは、こうした要件を満たすために開発されました。

PCIeは、従来の並列バス方式からシリアル通信方式へと進化しました。さらに、各デバイスが専用の通信路(ポイントツーポイント接続)を持ち、レーン数を柔軟に拡張できるため、高速かつ柔軟なデータ転送が可能です。

PCIeは、都市の高速道路のように複数のレーンを使って、データを同時に送受信します。世代が進むごとに1レーンあたりの転送速度も向上しており、複数レーンを組み合わせることで、より大容量のデータを高速にやり取りできるのが特徴です。

PCIe高速道路のイメージ

なぜPCIからPCIeへ?並列バスの限界と解決策

PCI(Peripheral Component Interconnect)は1992年に登場したもので、コンピューターの機能を拡張するために使われる標準的なインターフェイス規格です。PCIは並列バス方式を採用し、複数のデバイスが同じバスを共有していました。しかし、この仕組みにはいくつかの課題がありました。

-

帯域幅の制限:複数のデバイスが同じバスを共有するため、通信速度が制限されやすい。

-

遅延の増加:信号同士が干渉したり、タイミング同期が難しく、通信に遅延が生じやすい。

-

ノイズ耐性が低い:配線が密集しているため、外部ノイズや隣接信号の干渉(クロストーク)の影響を受けやすい。

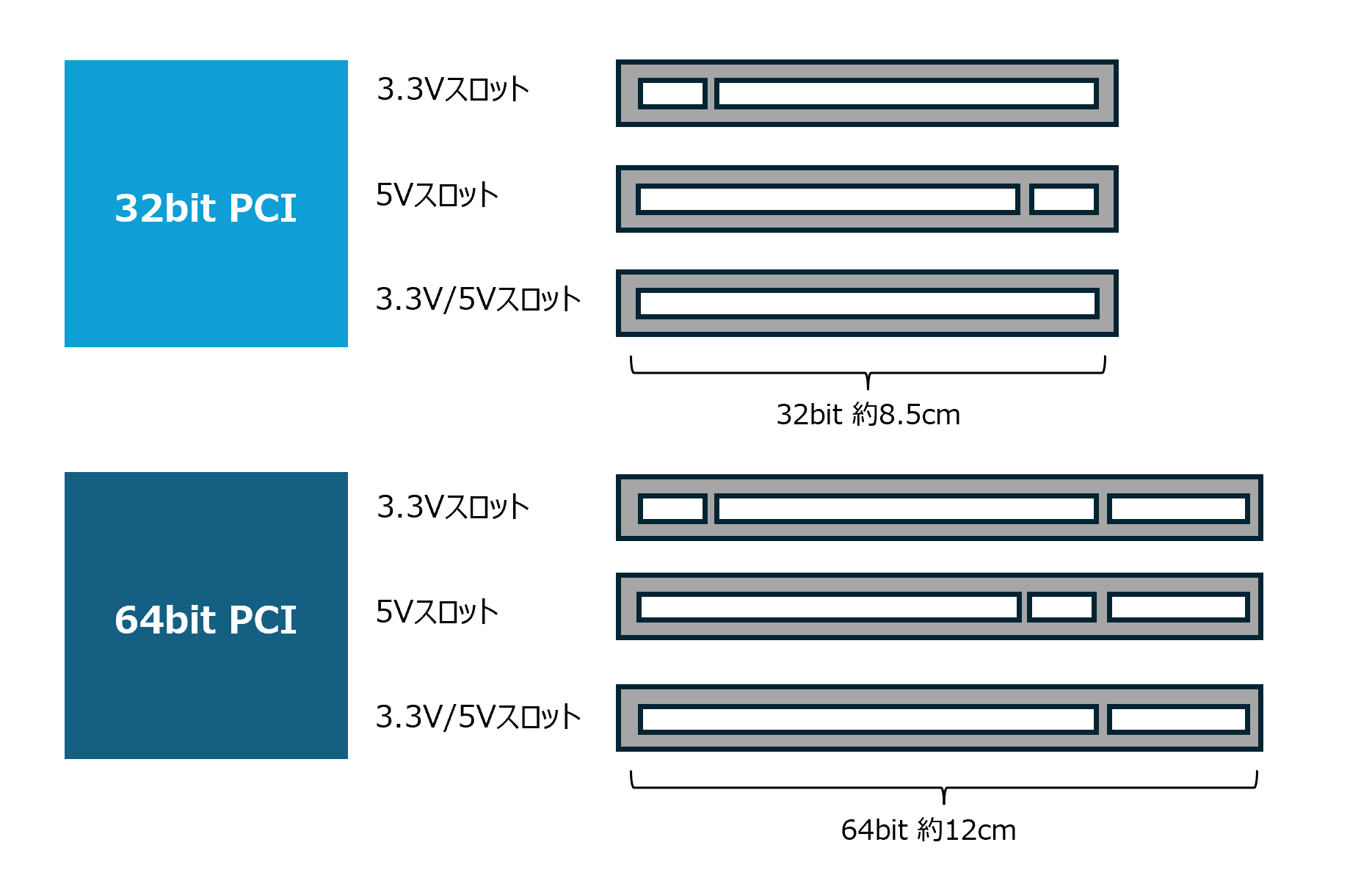

PCIとPCIeスロット

これらの問題を解決するために、2003年にPCI

Express(PCIe)が登場しました。PCIeは従来のPCIの制約を克服し、通信方式や拡張性など多くの点で進化しました。PCIeはPCIの後継ですが、コネクター形状や電気仕様が異なるため、物理的な互換性はありません。

PCIeの特徴をまとめました。

-

シリアル通信方式

PCIeでは、各デバイスが専用の通信路(ポイントツーポイント)を持つため、帯域幅の競合が起きにくくなっています。また、差動通信を採用しているため、外部ノイズの影響を受けにくく、高い信頼性を実現しています。 -

スケーラビリティ

PCIeは、x1、x4、x8、x16などレーン数を柔軟に選べるため、用途に応じて性能を拡張できます。 -

高速性

PCIeは世代を重ねるたびに転送速度が大きく向上しており、最新世代ではx16構成で100GB/s以上の高速通信が可能です。これにより、GPUやNVMe SSDなどの高性能デバイスの能力を最大限に引き出せます。

下記の表は、従来のPCIとPCIeの主な違いをまとめたものです。PCIeは伝送方式や速度、拡張性など、あらゆる面で大きく進化しています。

表1 PCI vs. PCIe

| 特性 | PCI(旧) | PCIe(新) |

|---|---|---|

| 伝送方式 | 並列伝送 | シリアル伝送 |

| 速度 | 低速(MB/s) | 高速(GB/s) |

| ノイズの耐性 | 弱い | 強い |

| 拡張構造 | バス型(共有) | ポイントツーポイント(専用) |

| 互換性 | なし | なし |

PCIとPCIeスロットの仕様解説

PCIとPCIeスロットは、どちらもPCやサーバーに拡張カードを接続するためのインターフェイスですが、構造と性能に大きな違いがあるため、両者のスロットに物理的な互換性はありません。ここでは、PCIとPCIeスロットの特徴を解説します。

PCIスロットの特徴

PCIは並列伝送方式を採用しており、バス型構造のため複数デバイスが通信路の帯域を共有します。

-

形状:長方形で、データバス幅は32bit(約8.5cm)と64bit(約12cm)の2種類。

-

電圧仕様:3.3Vまたは5V対応。キー(PCIスロットの切り欠き)位置で互換性を判別。

-

転送速度:32bitで約133MB/s(33MHz)、64bitで約533MB/s(66MHz)。

PCIスロットの形状

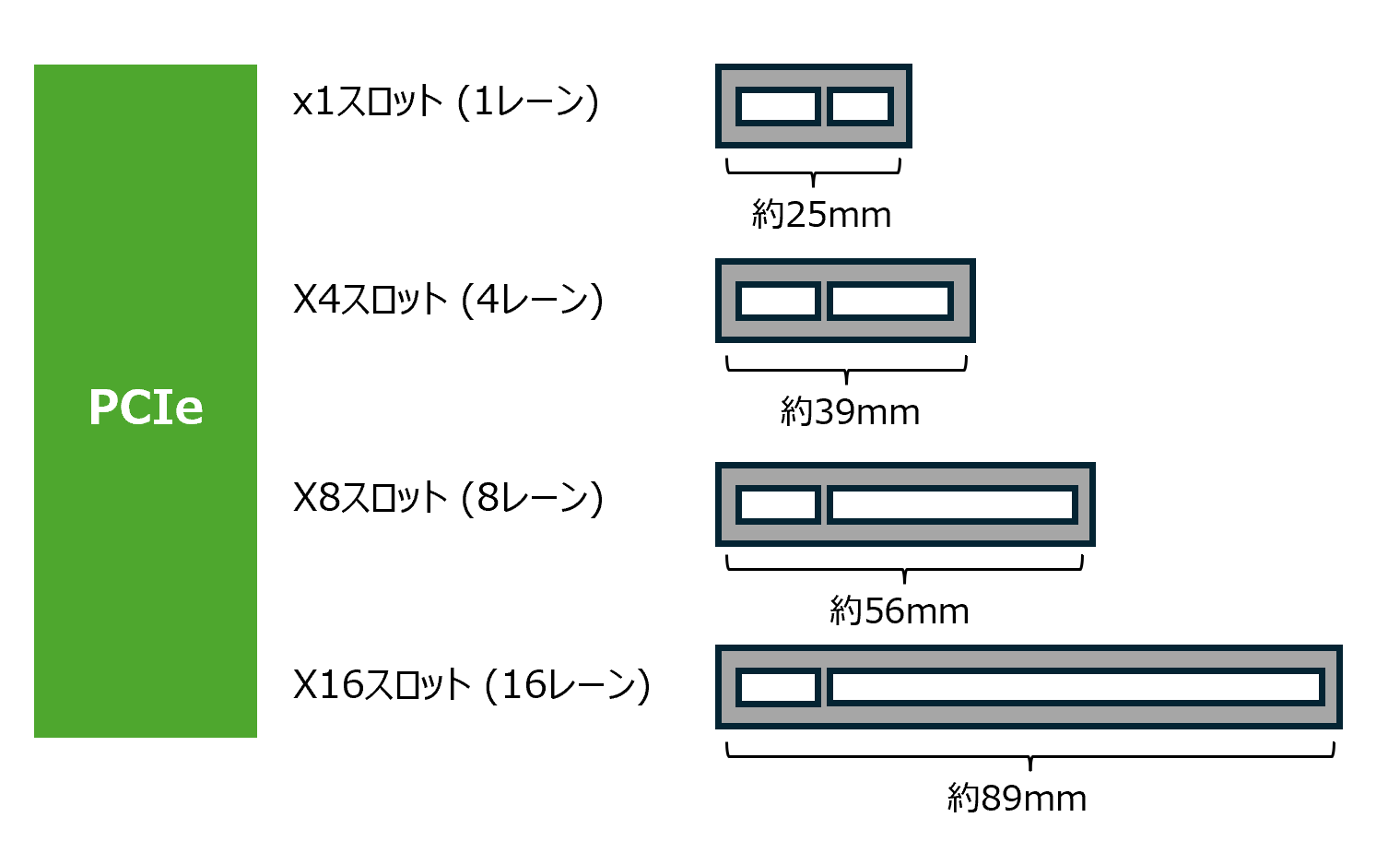

PCIeスロットの特徴

PCIの後継として開発されたPCIeはシリアル伝送方式を採用しており、各デバイスが専用レーンで接続されるため帯域を共有せず、高速でスケーラブルな性能を実現します。

- 形状:レーン数に応じて長さが異なる。x1(約25mm)、x4(約39mm)、x8(約56mm)、x16(約89mm)。

- 電圧仕様:信号電圧は3.3V、電源供給は12Vラインをサポート。キーによる電圧判別はない。

- 転送速度:1レーンあたりGen1 250MB/s~Gen6:8GB/s(x16で最大128GB/s)。

PCIeスロットの形状

PCIeスロットの互換性

PCIeインターフェイスを持つ拡張ボードは、物理的に同じレーン数、またはそれ以上のレーン数を備えたスロットに挿入できます。動作速度は、ボードとスロットのうち「低い方」に合わせて動作します。

例:x4対応のボード → x4スロット、またはx8スロットで使用可能。ただし、x1スロットには物理的に挿入できません。

世代別の帯域幅:Gen1~Gen6

PCIeは世代を重ねるごとに転送速度や帯域幅が飛躍的に向上しています。次の表で、各世代の特徴を比較しました。

表2 Generationごとの理論最大帯域幅

| 世代 | リリース年 | 転送速度(1レーン) | x16構成時の帯域幅 (片方向) |

|---|---|---|---|

| PCIe 1.0 | 2003年 | 250 MB/s | 約 4 GB/s |

| PCIe 2.0 | 2007年 | 500 MB/s | 約 8 GB/s |

| PCIe 3.0 | 2010年 | 1 GB/s | 約 16 GB/s |

| PCIe 4.0 | 2017年 | 2 GB/s | 約 32 GB/s |

| PCIe 5.0 | 2019年 | 4 GB/s | 約 64 GB/s |

| PCIe 6.0 | 2022年 | 8 GB/s | 約 128 GB/s |

注:表の数値は理論上の最大値であり、実際の通信速度はエンコード方式やオーバーヘッドの影響で低下する場合があります。

PCIeは世代間の後方互換を備えているため、上位世代デバイスと下位世代のスロットに接続することも可能です。ただし、通信速度は低い世代の帯域幅に制限されます。たとえば、PCIe 5.0デバイスをPCIe 3.0スロットに接続しても機能的に問題なく動作しますが、通信速度はPCIe 3.0の帯域幅に制限されます。さらに、実際の動作は物理設計や電力供給、BIOS設定、配線品質などからも影響を受けます。

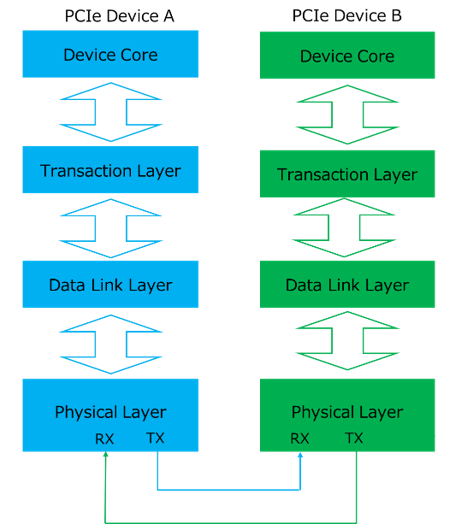

PCIeの司令塔:3階層構造

PCIeバスはシリアル接続方式を採用し、データはパケット(Packet)形式で転送されます。パケットは、トランザクション層(Transaction Layer)、データリンク層(Data Link Layer)、物理層(Physical Layer)の3つの階層を順に通過します。PCIeバスの階層構造を以下の図に示します。

PCIe階層構造及び送受信フロー

PCIeバスの階層構造は、ネットワークの階層モデルに似ていますが、すべてハードウェアで実装されている点が特徴です。PCIeでは、パケットはまずデバイスのコア(Device Core)で生成され、トランザクション層、データリンク層、物理層の順に送信されます。受信時も同様に、物理層からデータリンク層、トランザクション層を経て、最終的にデバイスコアに届きます。

-

トランザクション層:送受信のリクエストを管理し、パケットのヘッダーとデータペイロードを作成します。

-

データリンク層:パケットにシーケンス番号やエラーチェック情報を追加し、通信の信頼性を高めます。

-

物理層:実際の電気信号を使ってデータを送受信し、差動信号やデータのエンコーディングを行います。

この3層は、まるで3階建ての司令塔のように役割分担されています。各層が連携機能することで、PCIeの高速通信が安全かつ効率的に実現されるのです。

まとめ

PCI Express(PCIe)は、CPUと周辺機器をつなぐ高速な通信路として、現代のコンピューターやサーバーに不可欠な技術です。 シリアル通信方式やレーン構造の採用により、帯域幅や拡張性、高速性が大きく向上しました。さらに、3階層構造によって信頼性と効率性も両立しています。 次回は、PCIeのトポロジー構造や、その中で重要な役割を果たすPCIe Switchについて詳しく解説します。PCIeのトポロジーがどのように分岐し、複雑なシステムを支えるかを具体例で学びましょう。

お問い合わせ

関連技術コラム

関連製品情報

コネクテッドインテリジェントエッジ(Connected Intelligent Edge)を実現する Qualcomm IoT Application Processors

QualcommのIoT Application Processorsは、AIや5Gを活用し、ロボティクスやスマートカメラなどの多様なIoTソリューションを提供します。

- Qualcomm Technologies, Inc.

- NEXT Mobility

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

NXPの車載CAN/LINトランシーバー製品の特徴を徹底解説

車載ネットワーク製品をお探しのECU開発メーカー様向けに、車載環境の厳しい条件に耐えることのできる、NXPの車載CAN/LINトランシーバー製品の特徴について解説します。

- NXP Semiconductors N.V.

- NEXT Mobility

- ICT・インダストリアル

車載向け高速伝送技術GMSL2の特徴と製品ラインナップについて

より高画素なカメラの映像データを扱うことができるアナログ・デバイセズの次世代GMSL、GMSL2について特徴を説明します。

- Analog Devices, Inc.

- NEXT Mobility

- ICT・インダストリアル

NXPの車載統合マイコンS12 MagniVの魅力を徹底解説

NXPの統合マイコンS12 MagniVは、ECUの小型化と短期開発を実現し、車載システムの電動化に貢献します。S12 MagniVの特長や利点を解説しています。

- NXP Semiconductors N.V.

- NEXT Mobility

- ICT・インダストリアル

Qualcomm Automotive Connectivity Solution

Qualcommは、4G/5G、C-V2X、Wi-Fi、Bluetoothを活用した車載インフォテイメント向けの接続ソリューションを提供します。

- Qualcomm Technologies, Inc.

- NEXT Mobility

- ICT・インダストリアル

- スマートファクトリー・ロボティクス

GMSL2 設計の勘所

アナログ・デバイセズの次世代GMSL、GMSL2について特徴と、 設計の勘所を説明します。

- Analog Devices, Inc.

- NEXT Mobility